# GX3700/GX3700e GX3701/GX3702/GX3788

# User Configurable FPGA and Expansion Boards GXFPGA Software

User's Guide

Last Updated: December 16, 2016

## Safety and Handling

Each product shipped by Marvin Test Solutions is carefully inspected and tested prior to shipping. The shipping box provides protection during shipment, and can be used for storage of both the hardware and the software when they are not in use.

The circuit boards are extremely delicate and require care in handling and installation. Do not remove the boards from their protective plastic coverings or from the shipping box until you are ready to install the boards into your computer.

If a board is removed from the computer for any reason, be sure to store it in its original shipping box. Do not store boards on top of workbenches or other areas where they might be susceptible to damage or exposure to strong electromagnetic or electrostatic fields. Store circuit boards in protective anti-electrostatic wrapping and away from electromagnetic fields.

Be sure to make a single copy of the software diskette for installation. Store the original diskette in a safe place away from electromagnetic or electrostatic fields. Return compact disks (CD) to their protective case or sleeve and store in the original shipping box or other suitable location.

#### Warranty

Marvin Test Solutions products are warranted against defects in materials and workmanship for a period of 12 months. Software products and accessories are warranted for 3 months. Unless covered by software support or maintenance agreement. Marvin Test Solutions shall repair or replace (at its discretion) any defective product during the stated warranty period. The software warranty includes any revisions or new versions released during the warranty period. Revisions and new versions may be covered by a software support agreement. If you need to return a board, please contact Marvin Test Solutions Customer Technical Services department via <a href="http://www.marvintest.com/magic">http://www.marvintest.com/magic</a> the Marvin Test Solutions on-line support system.

#### If You Need Help

Visit our web site at <u>http://www.marvintest.com</u> for more information about Marvin Test Solutions products, services and support options. Our web site contains sections describing support options and application notes, as well as a download area for downloading patches, example, patches and new or revised instrument drivers. To submit a support issue including suggestion, bug report or question please use the following link: <a href="http://www.marvintest.com/magic">http://www.marvintest.com/magic</a>

You can also use Marvin Test Solutions technical support phone line (949) 263-2222. This service is available between 7:30 AM and 5:30 PM Pacific Standard Time.

#### Disclaimer

In no event, shall Marvin Test Solutions or any of its representatives be liable for any consequential damages whatsoever (including unlimited damages for loss of business profits, business interruption, loss of business information, or any other losses) arising out of the use of or inability to use this product, even if Marvin Test Solutions has been advised of the possibility for such damages.

#### Copyright

Copyright © 2003-2016, by Marvin Test Solutions, Inc. All rights reserved. No part of this document can be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Marvin Test Solutions.

# Trademarks

| ATEasy®, CalEasy, DIOEasy®, DtifEasy, WaveEasy                                              | Marvin Test Solutions (prior<br>name is Geotest - Marvin<br>Test Systems Inc.) |

|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Quartus                                                                                     | Altera Corporation                                                             |

| C++ Builder, Delphi                                                                         | Embarcadero Technologies<br>Inc.                                               |

| LabVIEW, LabWindows <sup>tm</sup> /CVI                                                      | National Instruments                                                           |

| Microsoft Developer Studio, Microsoft Visual C++, Microsoft Visual Basic, .NET, and Windows | Microsoft Corporation                                                          |

All other trademarks are the property of their respective owners.

# **Table of Contents**

| Safety and Handling             | i   |

|---------------------------------|-----|

| Warranty                        | i   |

| If You Need Help                | i   |

| Disclaimer                      | i   |

| Copyright                       | i   |

| Trademarks                      | ii  |

| Table of Contents               | iii |

| Chapter 1 - Introduction        | 1   |

| Manual Scope and Organization   | 1   |

| Manual Scope                    | 1   |

| Manual Organization             | 1   |

| Conventions Used in this Manual | 2   |

| Chapter 2 - Overview            | 3   |

| Introduction                    | 3   |

| Features                        | 3   |

| Applications                    | 4   |

| Board Description               | 5   |

| Architecture                    | 7   |

| Memory                          | 8   |

| PXI/PXIe and PC Connections     | 10  |

| Inter-FPGA Bus Interface Timing | 11  |

| DMA FIFO Interface Timing       | 12  |

| Specifications                  | 13  |

| Digital I/O Channel             | 13  |

| Expansion Board Interface       | 13  |

| Timing Source                   | 13  |

| User FPGA                       | 14  |

| Power                           | 14  |

| Environmental                   | 14  |

| Virtual Panel Description       | 15  |

| Virtual Panel Initialize Dialog | 16  |

| Virtual Panel Setup Page        | 17  |

| Virtual Panel I/O Page          |     |

| Virtual Panel DAQ Page (GX3788) | 19  |

| Virtual Panel About Page        | 21  |

| Chapter 3 - Installation and Connections               |    |

|--------------------------------------------------------|----|

| Getting Started                                        | 23 |

| Interfaces and Accessories                             | 23 |

| Packing List                                           | 23 |

| Unpacking and Inspection                               |    |

| System Requirements                                    | 24 |

| Installation of the GXFPGA Software                    | 24 |

| Setup Maintenance Program                              |    |

| Overview of the GXFPGA Software                        |    |

| Installation Folders                                   | 25 |

| Configuring Your PXI System using the PXI/PCI Explorer |    |

| Board Installation                                     | 27 |

| Before you Begin                                       | 27 |

| Electric Static Discharge (ESD) Precautions            |    |

| Installing a Board                                     | 27 |

| Plug & Play Driver Installation                        |    |

| Removing a Board                                       |    |

| GX3701 Connectors                                      |    |

| GX3701 J1 – Flex I/O Connector                         |    |

| GX3701 J2 – Flex I/O Connector                         |    |

| GX3701 J3 – Flex I/O Connector                         |    |

| GX3701 J4 – Flex I/O Connector                         |    |

| GX3788 Connectors                                      |    |

| GX3788 J1 – Flex I/O Bank A Connector                  |    |

| GX3788 J2 – Flex I/O Bank D Connector                  |    |

| GX3788 J3 – Flex I/O Bank B Connector                  |    |

| GX3788 J4 – Flex I/O Bank C Connector                  |    |

| Jumpers                                                |    |

| hapter 4 - Programming the Board                       |    |

| The GXFPGA Driver                                      | 43 |

| Programming Using C/C++ Tools                          |    |

| Programming Using Visual Basic and Visual Basic .NET   |    |

| Programming Using Pascal/Delphi                        |    |

| Programming GXFPGA Boards Using ATEasy®                | 44 |

| Programming Using LabVIEW and LabVIEW/Real Time        | 44 |

| Using and Programming under Linux                      | 44 |

| Using the GXFPGA driver functions                      | 45 |

| Initialization, HW Slot Numbers and VISA Resource                            | 45 |

|------------------------------------------------------------------------------|----|

| Board Handle                                                                 | 46 |

| Reset                                                                        | 46 |

| Error Handling                                                               | 46 |

| Driver Version                                                               | 46 |

| Programming Examples                                                         | 46 |

| Distributing the Driver                                                      | 46 |

| Chapter 5 - GXFPGA Schematic Entry Tutorial                                  |    |

| Introduction                                                                 | 47 |

| Downloading Altera Design FPGA Design Tools                                  | 47 |

| Create New Project                                                           | 48 |

| Device Selection                                                             | 48 |

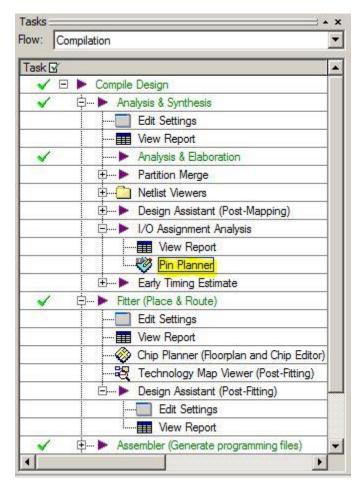

| Pin Assignment Setup                                                         | 49 |

| Pin Assignments Table                                                        | 49 |

| Schematic entry project                                                      | 51 |

| Creating Design File with Schematic Entry                                    | 53 |

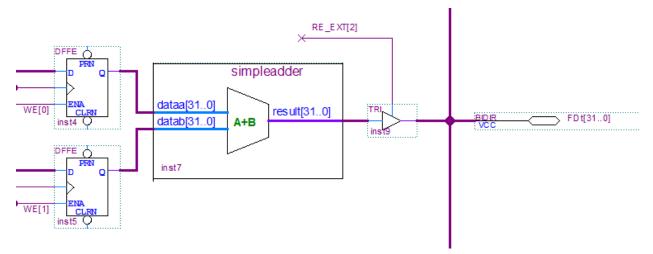

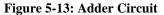

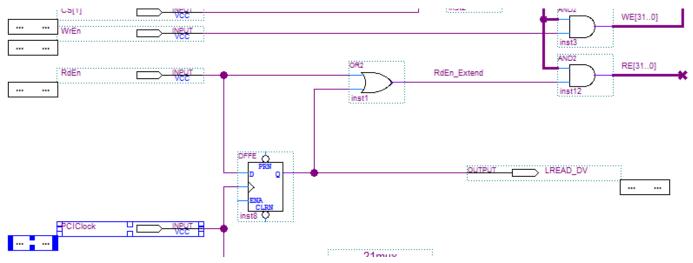

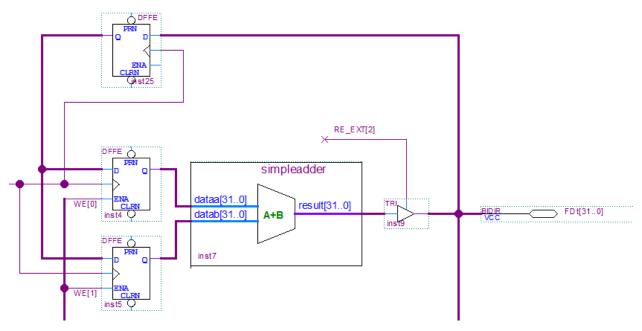

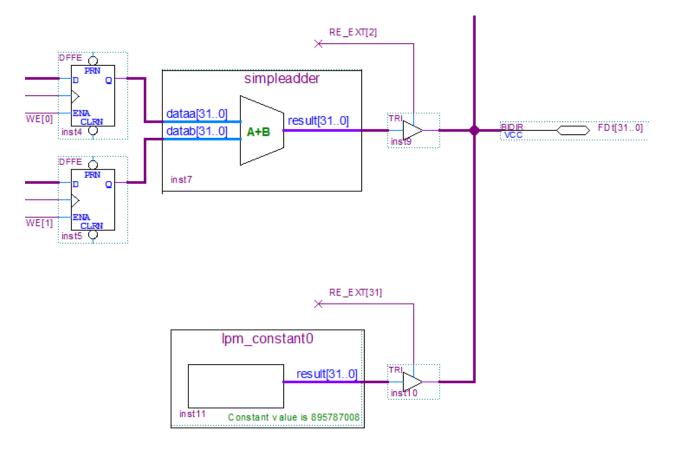

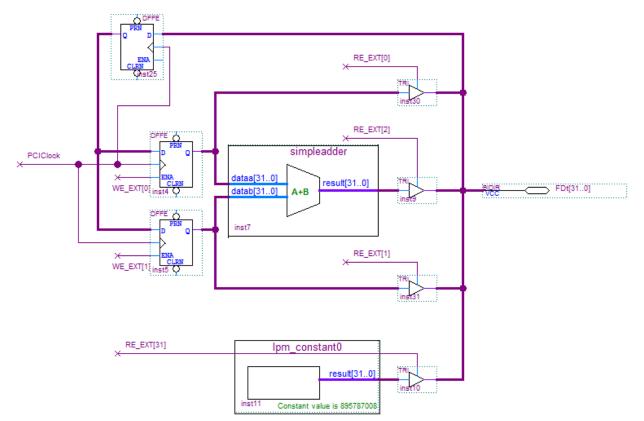

| Phase 1: Creating the FPGA design - 32 bit Full Adder                        | 53 |

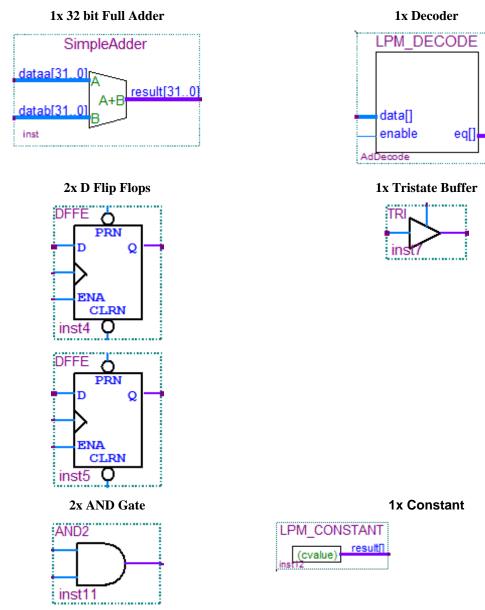

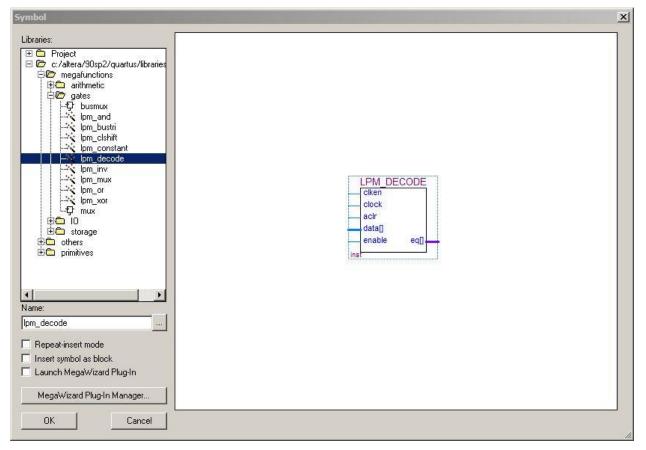

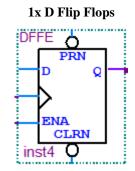

| Components Used                                                              | 53 |

| Schematic view                                                               | 54 |

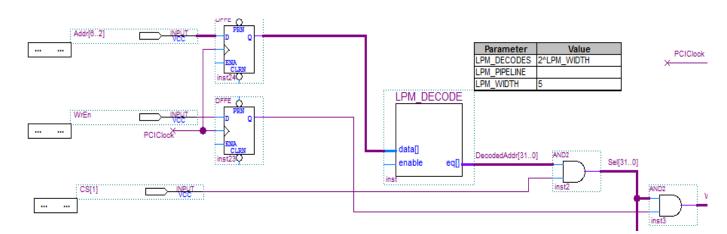

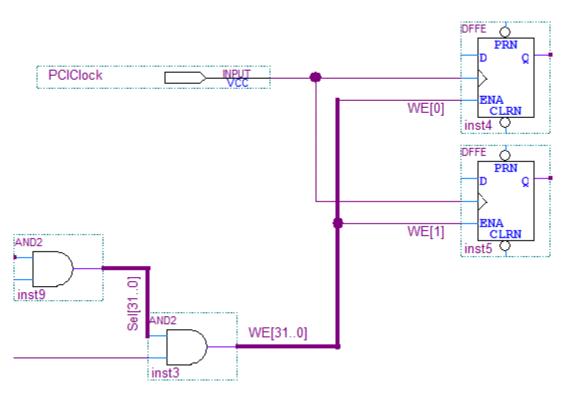

| Design                                                                       | 55 |

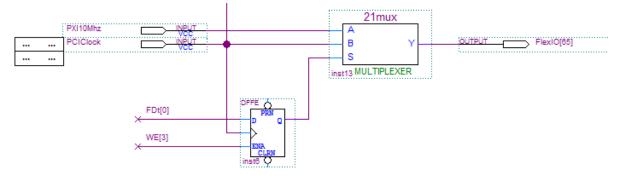

| Phase 2: Creating the FPGA Design - 2 to 1 Clock Mux                         | 66 |

| Components Used                                                              | 66 |

| Design                                                                       | 66 |

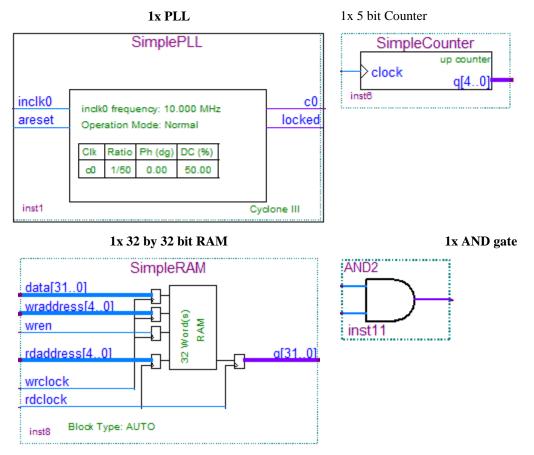

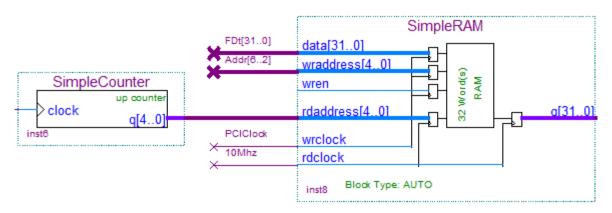

| Phase 3: Creating the FPGA Design - 32 bit Dynamic Digital Pattern Sequencer | 67 |

| Components Used                                                              | 67 |

| Design                                                                       | 67 |

| Configure Project to Output SVF and RPD Files                                | 71 |

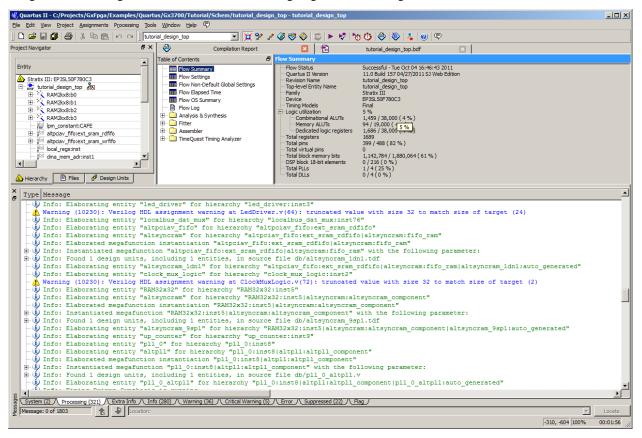

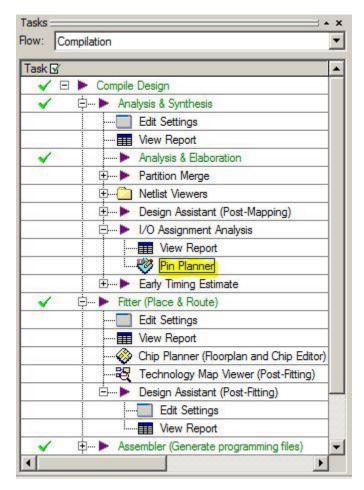

| Compile an Example Project and Build RPD and SVF Files                       | 73 |

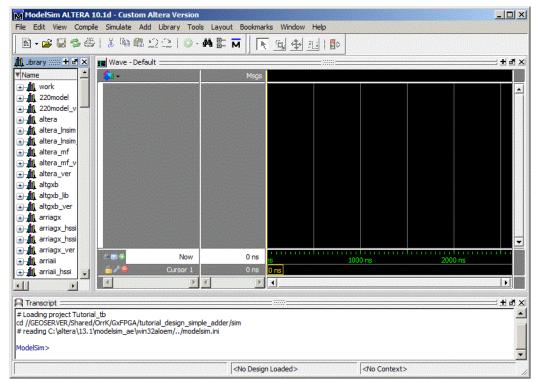

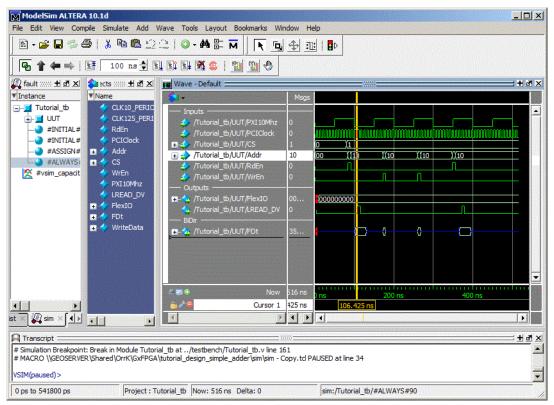

| Simulating the Design                                                        | 75 |

| Load Gx3700 with SVF File                                                    |    |

| Testing the Design                                                           | 79 |

| Adder Testing                                                                | 79 |

| Clock Mux Testing                                                            | 79 |

| Digital Sequencer Testing                                                    | 80 |

| Chapter 6 - GXFPGA Verilog Tutorial                                          |    |

| Introduction                                                                 | 81 |

| Downloading Altera Design FPGA Design Tools                                  | 81 |

| Create New Project                                     |    |

|--------------------------------------------------------|----|

| Device Selection                                       |    |

| Pin Assignment Setup                                   |    |

| Pin Assignments Table                                  |    |

| Verilog project                                        | 85 |

| Creating Design File with Verilog                      |    |

| Phase 1: Creating the FPGA design - 32 bit Full Adder  |    |

| Components Used                                        |    |

| Top-level Verilog file                                 |    |

| Top-level inputs and outputs                           |    |

| Phase 2: Creating the FPGA Design - 2 to 1 Clock Mux   | 95 |

| Design                                                 | 95 |

| Configure Project to Output SVF and RPD Files          | 96 |

| Compile an Example Project and Build RPD and SVF Files |    |

| Load Gx3700 with SVF File                              |    |

| Testing the Design                                     |    |

| Adder Testing                                          |    |

| Clock Mux Testing                                      |    |

| Chapter 7 - GXFPGA VHDL Tutorial                       |    |

| Introduction                                           |    |

| Downloading Altera Design FPGA Design Tools            |    |

| Create New Project                                     |    |

| Device Selection                                       |    |

| Pin Assignment Setup                                   |    |

| Pin Assignments Table                                  |    |

| Schematic entry project                                |    |

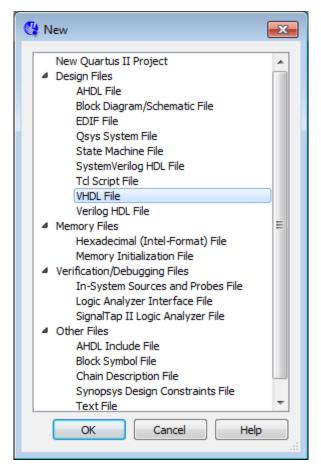

| Creating Design File with VHDL                         |    |

| Phase 1: Creating the FPGA design - 32 bit Full Adder  |    |

| Components Used                                        |    |

| Top-level VHDL file                                    |    |

| Top-level inputs and outputs                           |    |

| Phase 2: Creating the FPGA Design - 2 to 1 Clock Mux   |    |

| Design                                                 |    |

| Configure Project to Output SVF and RPD Files          |    |

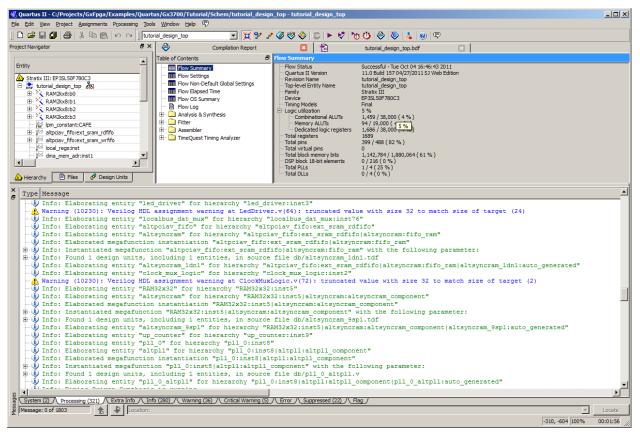

| Compile an Example Project and Build RPD and SVF Files |    |

| Simulating the Design                                  |    |

| Load Gx3700 with SVF File                              |    |

| Testing the Design                                                     |     |

|------------------------------------------------------------------------|-----|

| Adder Testing                                                          |     |

| Clock Mux Testing                                                      | 131 |

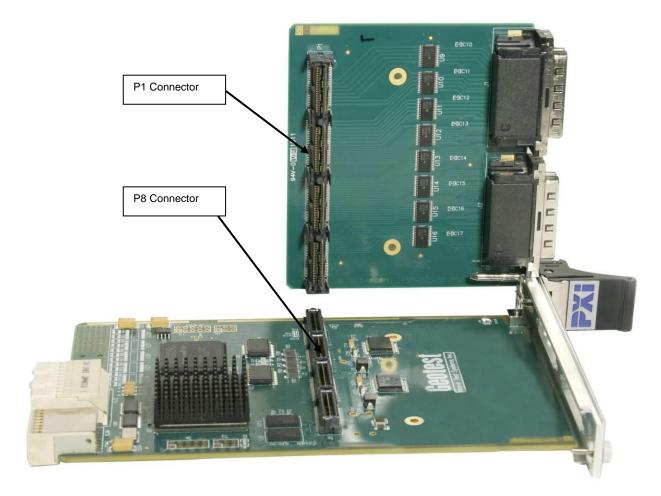

| Chapter 8 - GX3700 Expansion Boards                                    | 133 |

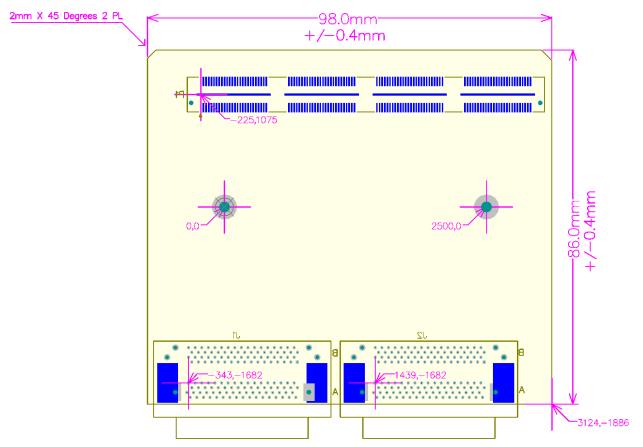

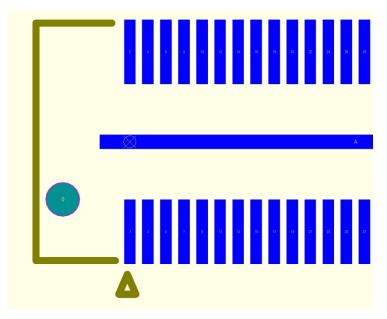

| Expansion Board Design Guide                                           |     |

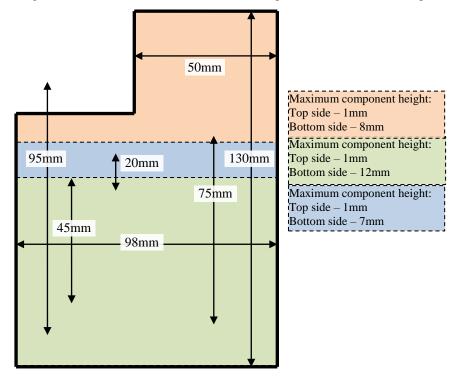

| Mechanical Layout Guide                                                |     |

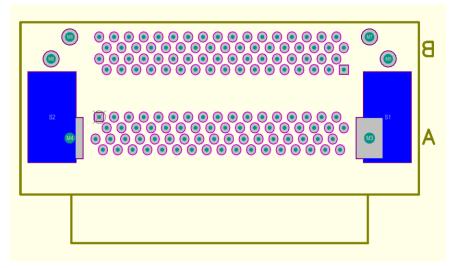

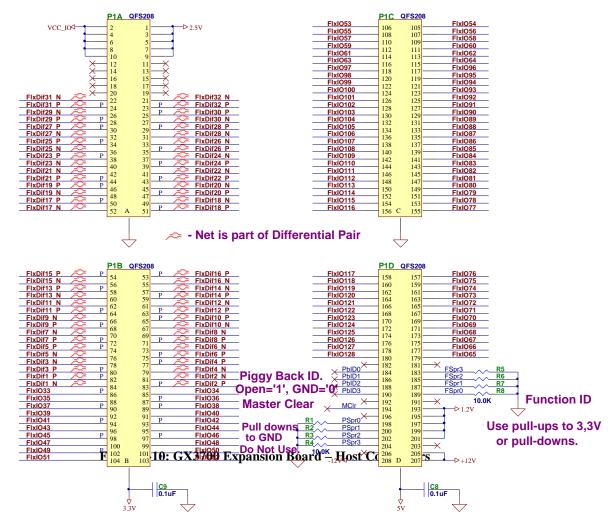

| Expansion Board Connectors and Electrical Requirements                 | 141 |

| P1 Expansion Board Connector Pin Assignment                            | 142 |

| GX3701 Expansion Board                                                 | 148 |

| GX3701 Programming                                                     | 148 |

| GX3701 Expansion Board Specification                                   | 148 |

| GX3702 Expansion Board                                                 | 149 |

| J1 – Flex I/O Bank A Connector                                         | 149 |

| J2 – Flex I/O Bank B Connector                                         |     |

| J3 – Flex I/O Bank C Connector                                         |     |

| J4 – Flex I/O Bank D Connector                                         | 151 |

| GX3702 Expansion Board Specification                                   | 151 |

| GX3788 Expansion Board                                                 | 152 |

| GX3788 Programming                                                     | 152 |

| GX3788 Digital and Analog Multi-Function Expansion Board Specification |     |

| Chapter 9 - Function Reference                                         | 155 |

| Introduction                                                           | 155 |

| GXFPGA Functions                                                       | 156 |

| GxFpgaDiscardEvents                                                    | 159 |

| GxFpgaDmaFreeMemory                                                    |     |

| GxFpgaDmaGetTransferStatus                                             | 161 |

| GxFpgaDmaTransfer                                                      |     |

| GxFpgaGetBoardSummary                                                  |     |

| GxFpgaGetBoardType                                                     | 164 |

| GxFpgaGetEepromSummary                                                 | 165 |

| GxFpgaGetDriverSummary                                                 | 166 |

| GxFpgaGetErrorString                                                   | 167 |

| GxFpgaGetExpansionBoardID                                              | 170 |

| GxFpgaInitialize                                                       | 171 |

| GxFpgaInitializeVisa                                                   |     |

| GxFpgaLoad                                                             |     |

| GxFpgaLoadFromEeprom                                                   | 174 |

|                                                                        |     |

| GxFpgaLoadStatus                      |  |

|---------------------------------------|--|

| GxFpgaLoadStatusMessage               |  |

| GxFpgaPanel                           |  |

| GxFpgaRead                            |  |

| GxFpgaReadRegister                    |  |

| GxFpgaReset                           |  |

| GxFpgaSetEvent                        |  |

| GxFpgaUpgradeFirmware                 |  |

| GxFpgaUpgradeFirmwareStatus           |  |

| GxFpgaWaitOnEvent                     |  |

| GxFpgaWrite                           |  |

| GxFpgaWriteRegister                   |  |

| Gx3788Initialize                      |  |

| Gx3788InitializeVisa                  |  |

| Gx3788Reset                           |  |

| Gx3788GetBoardSummary                 |  |

| Gx3788GetCalibrationInfo              |  |

| Gx3788AnalogInGetGroundSource         |  |

| Gx3788AnalogInMeasureChannel          |  |

| Gx3788AnalogInScanGetChannelListIndex |  |

| Gx3788AnalogInScanGetCount            |  |

| Gx3788AnalogInScanGetLastRunCount     |  |

| Gx3788AnalogInScanGetSampleRate       |  |

| Gx3788AnalogInScanIsRunning           |  |

| Gx3788AnalogInScanReadMemoryRawData   |  |

| Gx3788AnalogInScanReadMemoryVoltages  |  |

| Gx3788AnalogInScanSetChannelListIndex |  |

| Gx3788AnalogInScanSetCount            |  |

| Gx3788AnalogInScanSetSampleRate       |  |

| Gx3788AnalogInScanStart               |  |

| Gx3788AnalogInSetGroundSource         |  |

| Gx3788AnalogOutGetOutputState         |  |

| Gx3788AnalogOutGetVoltage             |  |

| Gx3788AnalogOutReset                  |  |

| Gx3788AnalogOutSetOutputState         |  |

| Gx3788AnalogOutSetVoltage             |  |

| Gx3788PioGetPort                      |  |

| Index                            |  |

|----------------------------------|--|

| Gx3788TriggerSetOutputLevel      |  |

| Gx3788TriggerReadInputLevel      |  |

| Gx3788TriggerGetOutputLevel      |  |

| Gx3788PioSetPortDirection        |  |

| Gx3788PioSetPortChannelDirection |  |

| Gx3788PioSetPortChannel          |  |

| Gx3788PioSetPort                 |  |

| Gx3788PioResetPortChannel        |  |

| Gx3788PioResetPort               |  |

| Gx3788PioReadPortChannel         |  |

| Gx3788PioReadPort                |  |

| Gx3788PioGetPortDirection        |  |

| Gx3788PioGetPortChannelDirection |  |

| Gx3788PioGetPortChannel          |  |

X GX3700 User's Guide

# **Chapter 1 - Introduction**

## Manual Scope and Organization

#### Manual Scope

The purpose of this manual is to provide all the necessary information to install, use, and maintain the GX3700 / GX3700e instruments. This manual assumes the reader has a general knowledge of PC based computers, Windows operating systems, and some understanding of digital I/O.

This manual also provides programming information using the GX3700 driver (referred in this manual **GXFPGA**). Therefore, good understanding of programming development tools and languages may be necessary. The **GXFPGA** function library supports both the GX3700 (PXI Hybrid slot compatible) and GX3700e (PXI Express) versions of the module. The terms GX3700 and GX3700e are used interchangeably throughout the manual, any differences are noted specifically.

#### **Manual Organization**

The GX3700 manual is organized in the following manner:

| Chapter                                           | Content                                                                                                                                                                                                 |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 1 - Introduction                          | Introduces the GX3700 manual. Lists all the supported board and shows warning conventions used in the manual.                                                                                           |

| Chapter 2 – Overview                              | Describes the GX3700 features, board description, its architecture, specifications and the panel description and operation.                                                                             |

| Chapter 3 –Installation<br>and Connections        | Provides instructions on how to install a GX3700board and the GXFPGA software.                                                                                                                          |

| Chapter 4 –<br>Programming the Board              | Provides a list of the GXFPGA software driver files, general purpose and generic driver functions, and programming methods. Discusses supported application development tools and programming examples. |

| Chapter 5 – GXFPGA<br>Schematic Entry<br>Tutorial | Provides an example of how to use the Quartus II's Schematic Entry method to design<br>and FPGA and then load and test the design using the GXFPGA panel.                                               |

| Chapter 6 – GXFPGA<br>Verilog Tutorial            | Provides an example of how to use Quartus II and Verilog to design an FPGA and then load and test the design using the GXFPGA panel.                                                                    |

| Chapter 7 – GXFPGA<br>VHDL Tutorial               | Provides an example of how to use Quartus II and VHDL to design an FPGA and then load and test the design using the GXFPGA panel.                                                                       |

| Chapter 8 – Expansion<br>Boards                   | Describes how to design a GX3700 expansion board and describes several standard expansion boards available from Marvin Test Solutions.                                                                  |

| Chapter 9 – Functions<br>Reference                | Provides a list of the GX3700 driver functions. Each function description provides syntax, parameters, and any special programming comments.                                                            |

# **Conventions Used in this Manual**

| Symbol Convention | Meaning                                                                             |

|-------------------|-------------------------------------------------------------------------------------|

| <b>?</b>          | Static Sensitive Electronic Devices. Handle Carefully.                              |

| STOP              | Warnings that may pose a personal danger to your health. For example, shock hazard. |

|                   | Cautions where computer components may be damaged if not handled carefully.         |

| TIP               | Tips that aid you in your work.                                                     |

| Formatting<br>Convention | Meaning                                                                                                                 |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Monospaced Text          | Examples of field syntax and programming samples.                                                                       |

| Bold type                | Words or characters you type as the manual instructs. For example: function or panel names.                             |

| Italic type              | Specialized terms. Titles of other reference books. Placeholders for items you must supply, such as function parameters |

# **Chapter 2 - Overview**

### Introduction

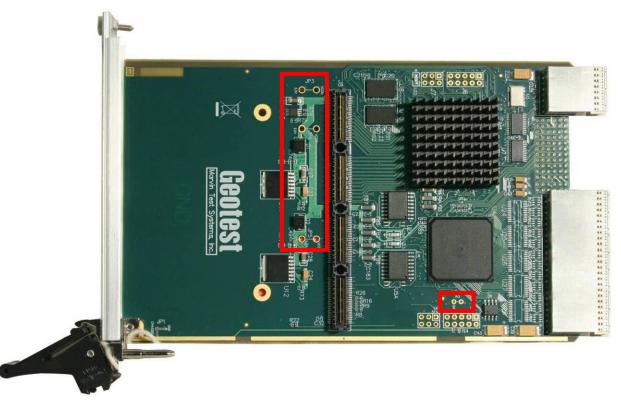

The GX3700 / GX3700e is a user configurable, FPGA based, 3U PXI / PXI Express card which offers 160 digital I/O signals which can be configured for single-ended or differential interfaces. The card employs the Altera Stratix III FPGA, which can support data rates up to 1.2 Gb/s (SerDes interface) and features over 65,000 logic elements and 2.636 Kb of memory. The GX3700 / GX3700e is supplied with an expansion board, GX3701 – Flex I/O Feed Through Module, providing access to the FPGA's 160 I/Os. Alternatively, users can design their own custom expansion cards for specific applications eliminating the need for additional external boards which are cumbersome and physically difficult to integrate into a test system. The design of the FPGA is done by using Altera's free Quartus II Web Edition tool set. Once the user has compiled the FPGA design, the configuration file can be loaded directly into the FPGA or via an on-board EEPROM.

#### Features

The GX3700 / GX3700e's digital I/O signals are 5 volt tolerant. Logic families supported by the I/O interface include LVTTL, LVDS and LVCMOS. The FPGA's I/Os includes 160 single ended I/O with support for 32 differential pairs, 4 dedicated global clock inputs (2 differential pairs), and various VCCIO voltages. At power-up, all I/Os will be isolated from the UUT. The FPGA device supports up to four phase lock loops (PLL) for clock synthesis, clock generation and for support of the I/O interface. An on-board 80 MHz oscillator is available for use with the FGPA device or alternatively, the PXI 10 MHz or 100 MHz clock can be used as a clock reference by the FPGA.

The FPGA has access to all of the PXI Express bus resources including the PXI 10 MHz clock, PXIe 100 MHz clock, PXIe Sync100, PXIe DStar triggers, the local bus, and the PXI triggers; allowing the user to create a custom instrument which incorporates all of the PXI Express bus resources. The GX3700's FPGA has access to all of the PXI Hybrid slot compatible resources including PXI 10 MHz clock, the local bus, and the PXI triggers Control and access to the FPGA is provided via the GX3700 / GX3700e's driver which includes tools for downloading the compiled FPGA code as well as register read and write functionality.

The GX3700 / GX3700e include the provision to add a daughter board which will provide additional flexibility for those users who wish to design their own custom interfaces for specific applications.

Communication between the customer-programmable FPGA and the PXI/PXIe bus is implemented via a dedicated FPGA device (Interface FPGA). The Interface FPGA contains control and status registers for the board and provides in-system programmability of the customer-programmable FPGA. The Interface FPGA interfaces directly to the PXI/PXIe bus and will decode/encode the bus protocol.

The GX3700 has external SRAM, flash, and an external clock source that is accessible by the customer.

The GX3700 employs the Altera Stratix III 780 pin device. Key features for the Altera device includes:

- 47,500 logic elements (LEs) and 1.88Mbits of memory

- Supports up to four phase-locked loops (PLLs) for clock synthesis, clock generation and support of I/O interfaces

- Up to five outputs per PLL can be accessed

- Dynamically reconfigurable logic supports programmable phase shift, frequency multiplication/division, and in-system frequency re-programming without reconfiguring the device

- Support for high-speed external memory interfaces including DDR, DDR2, SDR, SDRAM, and QDRII SRAM at up to 400 megabits per second (Mbps)

- 327 I/O pins arranged in eight I/O banks that support a wide range of industry I/O standards

- Supports up to 875 Mbps receive and 840 Mbps transmit LVDS communications data rates

- Support for Bus LVDS (BLVDS), LVDS, RSDS®, mini-LVDS and PPDS® differential I/O standards

- Supported I/O standards include LVTTL, LVCMOS, SSTL, HSTL, PCI, PCI-X, LVPECL, LVDS, mini-LVDS, RSDS, and PPDS; PCI Express Base

- 160 single ended I/Os.

- 32 differential pairs.

- 4 dedicated global clock inputs (2 differential pairs).

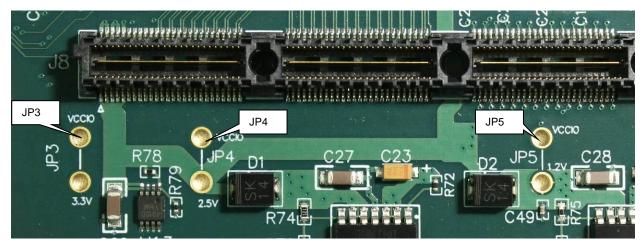

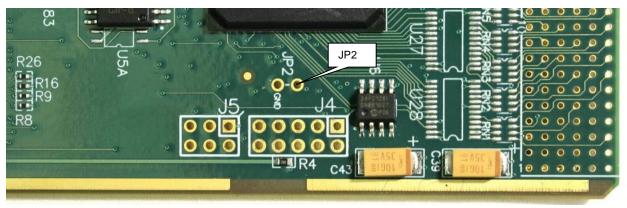

- VCCIO can be preset using on-board jumpers to 1.2V, 2.5V, or 3.3V.

- Internal FPGA SRAM (memory size depends on internal FPGA model installed)

- 1MB external SRAM in addition to internal FPGA SRAM.

- 16MB flash

- User controlled LED.

- Integrated DMA engine.

- All of PXI/PXIe instrumentation signals such as differential Star Trigger, SYNC100, CLK100, CLK10, local bus, trigger bus, and single-ended Star Trigger are available to customer.

# **Applications**

- Automatic Test Equipment (ATE) and Functional Test

- Data Acquisition

- Process Control

- Factory Automation

# **Board Description**

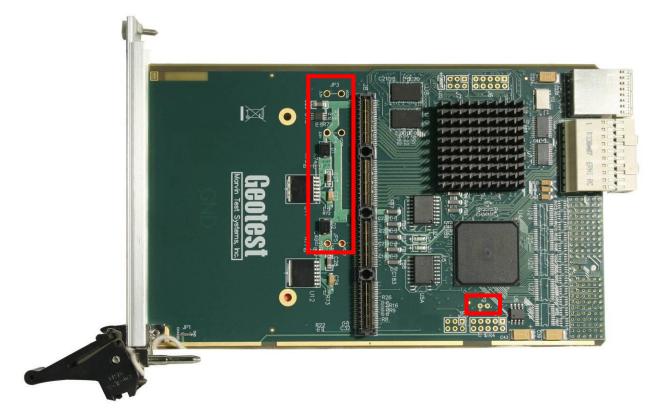

The GX3700 is a 3U PXI hybrid slot compatible instrument card that consists of 160 TTL I/O Channels divided into groups of 40 channels. Each of these groups is connected to a 68 pin SCSI type connector on the front panel of the instrument (J1-J4) using a daughter board module (GX3701). A short on JP7 will force the user FPGA to be configured automatically on boot up using the contents of the EEPROM. For more information about the connectors and jumpers and their location on the board refer to Chapter 3 – Installation and Connections.

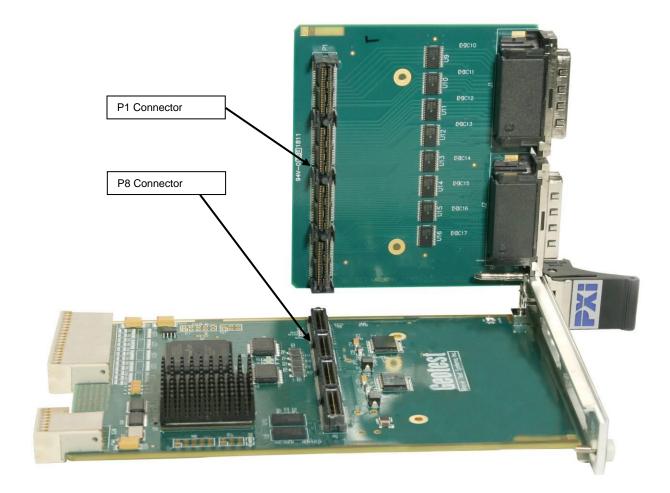

Figure 2-1: GX3700e Board with the GX3701 Module Mounted

Figure 2-2: GX3700 Board with the GX3701 Module Mounted

#### Architecture

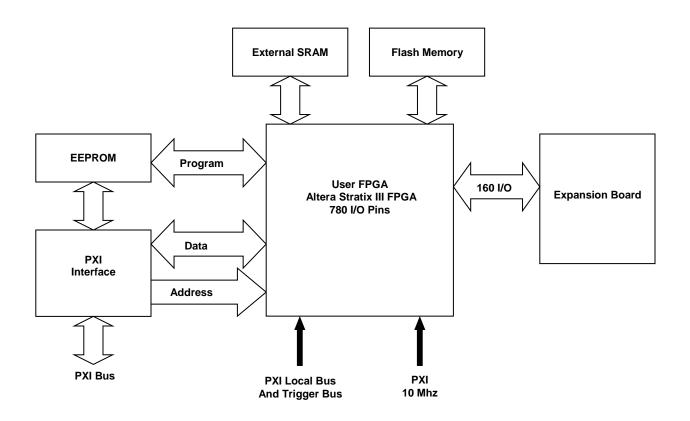

The GX3700 consists of a user programmable FPGA that can access external resources and peripherals such as the PCI bus, SRAM and flash memories. The user FPGA is an Altera Stratix III that can be programmed directly through the software driver or indirectly by the onboard EEPROM that can store a FPGA bit stream for later use. An Expansion board connects to the User FPGA to provide external I/O. The standard expansion board provides 160 I/O channels that are brought out to the front panel. The user may design custom expansion boards based on documentation provided by Marvin Test Solutions.

Figure 2-3: GX3700 Architecture

#### Memory

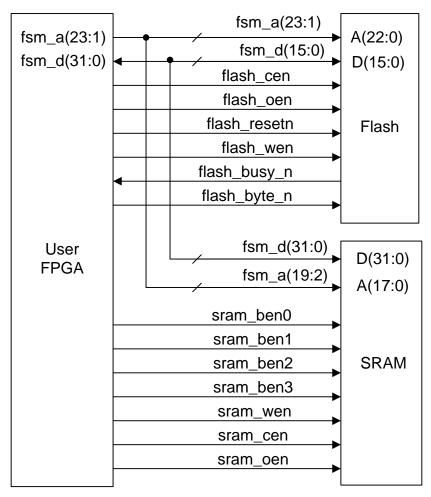

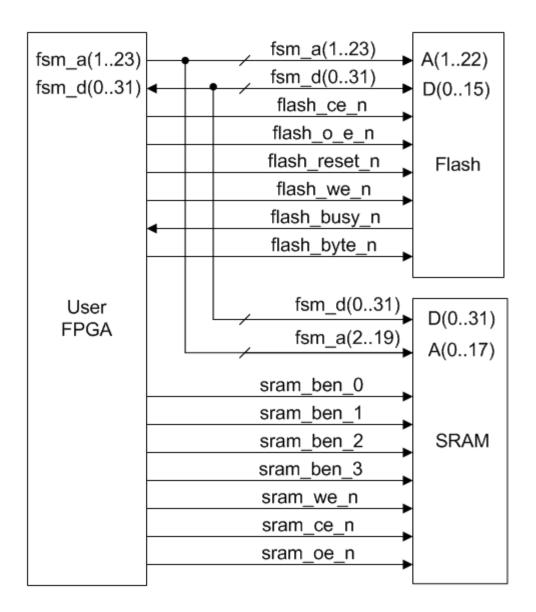

The Gx3700 has three types of memories, internal SRAM, external SRAM and Flash memory.

Figure 2-6 is a more detailed block diagram of the connections between the User's FPGA, the Flash and the SRAM

# GX3700/e Connections Between User FPGA, Flash, and SRAM

Figure 2-4: GX3700 / GX3700e Connections between User FPGA, Flash, and SRAM

#### **PXI/PXIe and PC Connections**

The User FPGA, Stratix III, can be configured either through the EEPROM or directly through the PXI Interface. It has access to PXI resources such as the local bus, trigger bus, and PXI 10 Mhz clock source and is also connected to the PXI Interface FPGA to give access to PCI resources and memory. This allows the User FPGA to communicate with the host system's operating system using the provided GXFPGA software library functions.

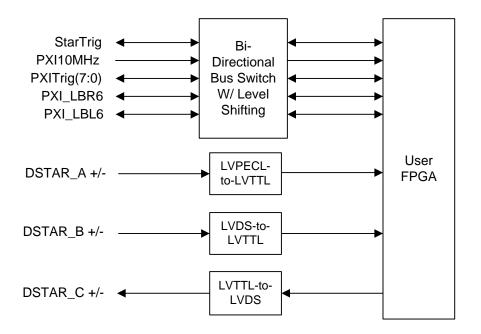

A more detailed diagram of the PXI/PXIe Signal Connections is shown below. It shows the different PXI/PXIe signals and how they are interfaced to the User FPGA.

The bi-directional bus switch with level shifting allows the PXI/PXIe signals to be interfaced to the User FPGA. The direction of the signals is controlled and determined by the signals from the User FPGA.

For example, to use the signal PXITrig(7), the user FPGA would be programmed as follows:

- 1. If this signal is only used as an input, define it inside the User FPGA as an input pin.

- 2. However, if the signal is used as an output only or a bidirectional I/O, define it as such in the User FPGA but make sure to drive the output to high impedance or tri-state level when the signal is not driving or is inactive.

In both of these cases the level translation and the direction of the signals are handled by the on-board bus switch.

Also shown are the buffers for the DSTAR\_A, DSTAR\_B and DSATR\_C signals. These buffers conform to the standard as required by the PXI Systems Alliance's PXI Express Hardware Specification Rev 1.0. Note that the DSTAR signals are only available with the GX3700e module.

Figure 2-5: PXI/PXIe Signal Connections

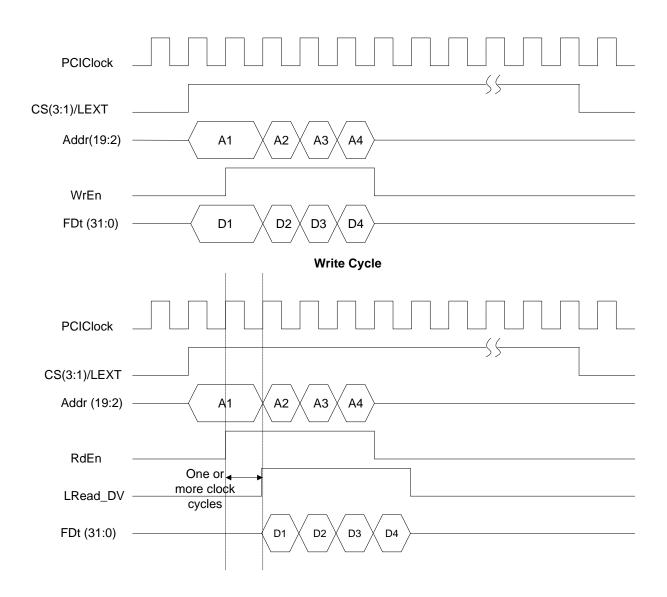

#### Inter-FPGA Bus Interface Timing

The Flex FPGA communicates with the PCI/PCIe host via the PXI/PXIe Bridge FPGA. The following figure shows the inter-FPGA timing diagram for communication between the two FPGAs.

#### **Read Cycle**

Figure 2-6 – Inter-FPGA Bus Interface Diagram

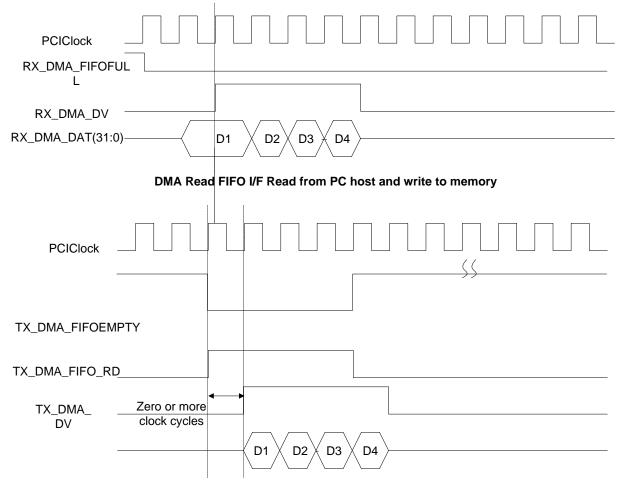

#### **DMA FIFO Interface Timing**

The PXI Bridge FPGA contains the DMA engine for transferring data between the Flex FPGA and the PCI/PCIe host. Unlike a Scatter-Gather DMA engine, this one will need a contiguous memory space.

There are two 32-bit buses between the PXI Bridge FPGA and the Flex FPGA for transmit and receive of DMA data.

For DMA write, the DMA controller will read data from the Flex FPGA and write this data to the host PC. The controller will only read data when it's in DMA write mode and will only read when the EMPTY signal is deasserted. The controller will only read up to the number of byte count specified for the DMA transfer and will not read more even if the FIFO is still empty.

For DMA read, the DMA controller will read data from the PC host and will write this data to the Flex FPGA. When in DMA read mode, the Flex FPGA must expect data and must store it. Otherwise, this data will be lost.

TX\_DMA\_DAT(31:0)

DMA Write FIFO I/F Read from memory and write to PC host

Figure 2-7: DMA FIFOs Timing Diagram

# Specifications

The following table outlines the specifications of the GX3700 / GX3700e.

## Digital I/O Channel

| Logic Families                    | LVTTL, LVDS, configurable for 1.2 / 2.5 / 3.3 V logic; 5 volt compatible ( programmable via the FPGA on a per pin basis) |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Output Current                    | $+\!/$ 12.0 mA, max. ( programmable via the FPGA on a per pin basis)                                                     |

| Input Leakage Current             | +/- 10 uA                                                                                                                |

| Power On State                    | Programmable by line, default is disconnect at power on                                                                  |

| Number of Channels                | 4 banks of 40 I/O signals. Direction is configurable on a per pin basis Disconnect on a per bank basis                   |

| Protection                        | Overvoltage: -0.5V to 7.0V (input) Short circuit: up to 8 outputs may be shorted at a time                               |

| Daughter Board User<br>Connectors | (4) SCSI III, VHDCI type, 68 pin female                                                                                  |

## **Expansion Board Interface**

| Board ID      | 4 bits                                                                         |

|---------------|--------------------------------------------------------------------------------|

| Digital I/O   | 160, each bank of 40 can be configured to bypass or access the expansion board |

| FPGA Flex I/O | 4 signals                                                                      |

| Master Clear  | From PXI interface                                                             |

| Power         | +/- 12 volts, +5 volts, +3.3 volts, +2.5 volts, +1.2 volts                     |

# **Timing Source**

| PXI 10 MHZ | PXI Bus                       |

|------------|-------------------------------|

| Internal   | 80 MHz oscillator, +/- 20 ppm |

## User FPGA

| FPGA Type       | Default:<br>3700: Stratix III, EP3SL50F780<br>3700e: Stratix III, EP3SL70F780<br>Check the instrument panel, About page for newer<br>versions.                                                                                              |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of PLLs  | Four                                                                                                                                                                                                                                        |

| Logic Elements  | 47,500                                                                                                                                                                                                                                      |

| Internal Memory | FPGA dependent:<br>EP3SL50: 2,133 Kb<br>EP3SL70: 2,636 Kb<br>EP3SL110: 4,875 Kb<br>EP3SL150: 6,390 Kb<br>EP3SL200: 10,646 Kb<br>EP3SL340: 18,381 Kb<br>EP3SE50: 5,625 Kb<br>EP3SE80: 6,683 Kb<br>EP3SE110: 8,727 Kb<br>EP3SLE260: 16,282 Kb |

#### Power

| 3.3 VDC                      | 400 mA (typ.); 1 A (Max.)   |

|------------------------------|-----------------------------|

| 5 VDC                        | 300 mA (typ.); 1.2 A (Max.) |

| 12 VDC (For Expansion Board) | Expansion Board Dependent   |

#### Environmental

| Operating Temperature | 0 to 50° C      |

|-----------------------|-----------------|

| Storage Temperature   | -20° C to 70° C |

| Size                  | 3U PXI          |

| Weight                | 200 g           |

### **Virtual Panel Description**

The GX3700 includes a virtual panel program, which enables full utilization of the various configurations and controlling modes. To fully understand the front panel operation, it is best to become familiar with the functionality of the board.

To open the virtual panel application, select **GX3700 Panel** from the **Marvin Test Solutions**, **GXFPGA** menu under the **Start** menu. The GX3700 virtual panel opens as shown here:

|       |                         |              | 1     | FPGA Board     |       | ? ×  |

|-------|-------------------------|--------------|-------|----------------|-------|------|

| Setup | 1/0                     | PIO          | About | ]              |       |      |

| FPGA  |                         | <u>e</u> epr | IOM [ | Load from EEPR | OM    | Load |

|       | OM<br>Jpload (<br>ame : | )n :         |       |                |       |      |

|       |                         |              |       |                |       |      |

|       |                         | Initializ    | e]    | Reset Apply    | Close | Help |

Figure 2-8: GX3700 Virtual Panel

**Initialize** – Opens the **Initialize Dialog** (see Initialize Dialog paragraph) in order to initialize the board driver. The current settings of the selected board will **not change after calling initialize**. The panel will reflect the current settings of the board after the Initialize dialog closes.

Reset - Resets the PXI board settings to their default state and clears the reading.

Apply – Applies changed settings to the board.

Close – Closes the panel. Closing the panel does not affect the board settings.

**Help** – Opens the on-line help window. In addition to the help menu, the caption shows a **What's This Help** button (?) button. This button can be used to obtain help on any control that is displayed in the panel window. To displays the What's This Help information click on the (?) button and then click on the control – a small window will displays the information regarding this control.

## Virtual Panel Initialize Dialog

The Initialize dialog initializes the driver for the selected board. The board settings **will not change** after initialize is called. Once initialized, the panel will reflect the current settings of the board.

The Initialize dialog supports two different device drivers that can be used to access and control the board:

Use Marvin Test Solutions' HW – This is the device driver installed by the setup program and is the default driver. When selected, the Slot Number list displays the available GX3700 boards installed in the system and their slots. The chassis, slots, devices and their resources are also displayed by the HW resource manager, PXI/PCI Explorer applet that can be opened from the Windows Control Panel. The PXI/PCI Explorer can be used to configure the system chassis, controllers, slots and devices. The configuration is saved to PXISYS.INI and PXIeSYS.INI located in the Windows folder. These configuration files are also used by VISA. The following figure shows the slot number 0x109 (chassis 1 Slot 9). This is the slot number argument (*nSlot*) passed by the panel when calling the driver GxFpgaInitialize function which is used to initialize the driver for the specified board.

|                        | Initialize                       | ? ×    |

|------------------------|----------------------------------|--------|

| <u>D</u> evice Driver: | ● Use HW/PXI Explorer 0 Use VISA | OK     |

| <u>S</u> lot Number:   | Chassis 1 Slot 9 (0x109) 🗸 🗸     | Cancel |

Figure 2-9: Initialize Dialog Box using Marvin Test Solutions' HW driver

2. Use VISA – This is a third-party device driver usually provided by National Instrument (NI-VISA). When selected, the **Resource** list displays the available boards installed in the system and their VISA resource address. The chassis, slots, devices and their resources are also displayed by the VISA resource manager, **Measurement & Automation** (NI-MAX) and by Marvin Test Solutions **PXI/PCI Explorer**. The following figure shows PXI9::13::INSTR as the VISA resource (PCI bus 9 and Device 13). This is a VISA resource string argument (*szVisaResource*) which is passed by the panel when calling the driver **GxFpgaInitializeVisa** function which initializes the driver for the specified board.

| Initialize            | ? ×                             |

|-----------------------|---------------------------------|

| ◯ Use HW/PXI Explorer | OK                              |

| PXI9::13::INSTR       | Cancel                          |

|                       | O Use HW/PXI Explorer  Use VISA |

Figure 2-10: Initialize Dialog Box using VISA resources

#### **Virtual Panel Setup Page**

After the board is initialized, the panel is enabled and will display the current setting of the board. The following picture shows the **Setup page** settings:

| !                                                                     | FPG                               | GA Boar       | d (0x108)                 |           | ?    | ×   |

|-----------------------------------------------------------------------|-----------------------------------|---------------|---------------------------|-----------|------|-----|

| Setup I/O<br>FPGA<br>O <u>V</u> olatile (<br><u>F</u> ile : \\geoserv | About<br>EEPROM<br>ver\projects\W |               | om EEPROM<br>rdware\3-Cor |           | Load |     |

|                                                                       | Firmware prog                     | gramming c    | ompleted suc              | cessfully |      |     |

| Last Upload Or<br>File Name :                                         | GX3700_us                         |               |                           |           |      |     |

|                                                                       |                                   |               |                           |           |      |     |

|                                                                       | Initialize                        | <u>R</u> eset | Apply                     | Close     | He   | elp |

Figure 2-11: GX3700 Virtual Panel – Setup page

The following controls are shown in the Setup page:

Volatile radio button: Select this radio button to load the File to the Volatile (current) FPGA configuration.

**EEPROM radio button:** Select this radio button to load File to the EEPROM FPGA.

**Load From EEPROM button:** Loads the volatile (current FPGA) with the FPGA configuration that is stored in the EEPROM

**File text box:** File path to the programming file intended to load the volatile FPGA or EEPROM. The File type must be Serial Vector File (.svf) for Volatile loading or Raw Programming Data (.RPD) file for EEPROM.

**Load Button:** Starts the loading process, either to the volatile FPGA or to the EEPROM, depending on which radio button the user selects.

EEPROM Last Updated On Text: Indicates the last time the EEPROM was loaded.

**EEPROM File Name Text:** Indicates the last file name that was written to the EEPROM.

**Expansion Board Bypass Checkboxes:** These checkboxes control the routing of each of the FPGA's I/O Banks. When the box is checked, it indicates that the I/O Bank will be connected directly to the I/O front connectors. If the box is unchecked, it indicates that the I/O Bank will be connected to the expansion board.

# Virtual Panel I/O Page

|          | Registers  | -     | 1 1 1 1 1 1 2 2 2 2 | Mem BAR2   | -     |

|----------|------------|-------|---------------------|------------|-------|

| Offset : | 0x0000     |       | Offset :            | 0x00000000 |       |

| Data :   | 0x00000000 | Write | Data :              | 0x00000000 | Write |

|          | -          | Read  |                     |            | Read  |

| FPGA     | Mem BAR3   |       | FPGA                | Mem BAR4   |       |

| Offset : | 0x00000000 | 1     | Offset :            | 0x00000000 | ]     |

| Data :   | 0x00000000 | Write | Data :              | 0x00000000 | Write |

|          |            | Read  |                     |            | Read  |

|          |            |       |                     |            |       |

|          |            |       |                     |            |       |

Clicking on the I/O tab will show the I/O page as shown in Figure 2-9: GX3700 Virtual Panel – I/O page

Figure 2-12: GX3700 Virtual Panel – I/O page

The following controls are shown in the I/O page:

**Offset Text Field:** The offset into the FPGA Register or Memory space (BAR2-4) in bytes. This field can be used with a decimal or hexadecimal value (prefix the value with 0x). The offset is limited to 0x400 bytes when reading the register space and 0x40000 bytes when reading the memory space. Offset must be specified on a 4-byte alignment.

Write Text Field: The 32-bit data (hexadecimal or decimal) to be written the specified offset in either FPGA Register or Memory space (BAR2-4).

Write Button: Write the 32-bit double word to either the FPGA Register or Memory space at the specified offset.

**Read Text Field:** The 32-bit data that has been read from the specified offset in either FGPA Register or Memory space. Value is specified in hexadecimal.

Read Button: Read the 32-bit double word from either the FPGA Register or Memory space at the specified offset.

### Virtual Panel DAQ Page (GX3788)

Clicking on the **DAQ** tab will show the **DAQ page** as shown in Figure 2-13: GX3788 Virtual Panel – DAQ page The **DAQ** tab only appears when the GX3788 daughter board is used.

| 💻 FPGA Boar | d (0x106)             |                    |                    | ? <mark>X</mark> |

|-------------|-----------------------|--------------------|--------------------|------------------|

| Setup I/O   | DAQ (GX3788)          | About              |                    |                  |

| Digital I/O |                       | -                  |                    |                  |

| Port 0      | ▼ Rea                 | adBack Data :      | 0xAA55FFFF         |                  |

| Reset Por   | + Dat                 | ta: 0              | xAA55AA55          | Set              |

|             | -                     | ection (1=Out) : 0 | ×FFFF0000          | Set              |

| Analog In - |                       |                    |                    |                  |

| Channel     | Mode                  | Range              | Measurement        | <u>_</u>         |

| 0           | Single Ended          | +/-13.60 V         | 1.112 V            | =                |

| 1           | Differential          | +/-13.60 V         | 1.733 V            |                  |

| 2           | Single Ended          | +/-13.60 V         | 1.871 V            |                  |

| 3           | Differential          | +/-5.12 V          | 0.896 V            |                  |

| 4           | Single Ended          | +/-13.60 V         | 2.606 V            |                  |

| 5           | Single Ended          | +/-10.24 V         | 2.453 V            |                  |

| 6           | Single Ended          | +/-13.60 V         | 2.161 V            | -                |

| Mod         | le : Single Ended     | ▼ Range            | +/-13.60 V         | -                |

| Ch (        | )-7: Analog Ground    | ▼ Ch 8-15          | 5: Digital Ground  | -                |

| Analog Outp | out                   |                    |                    |                  |

| 0: 0.000    | Set 2: 2.500          | Set 4: 4.500       | Set 6: 6.500       | Set              |

| 1: 1.000    | Set 3: 3.000          | Set 5: 5.000       | Set 7: 7.000       | Set              |

| 🔽 Ena       | ble All Channels Outp | uts R              | leset All Channels |                  |

|             | Initialize            | eset Apply         | Close              | Help             |

Figure 2-13: GX3788 Virtual Panel – DAQ page

The following controls are shown in the DAQ page:

#### **Digital I/O Group Box**

**Port Combo Box:** Select the digital I/O port (0-2) to configure. The output data and direction can be set and read for the selected digital port.

**Readback Field:** The 32-bit data that has been read from the specified digital port. This is an actual sampling of the digital line states at the selected digital port.

**Data Text Field:** The 32-bit output data (hexadecimal or decimal) to be written the specified digital port. A '1' bit signifies a logic high and a '0' bit signifies a logic low.

Set Button: Writes the Data field contents to the digital port selected.

**Direction Text Field:** The 32-bit direction data (hexadecimal or decimal) to be written to the specified digital port. A '1' bit signifies an output channel and a '0' bit signifies an input channel.

Set Button: Writes the Direction field contents to the digital port selected.

#### **Analog In Group Box**

**Analog In List:** Displays a continuously updating voltage measurement from each of the 16 analog input channels. In addition, each channels measurement mode and range are also shown.

Mode Combo Box: Sets the channel mode to use for a channel's measurement (single ended or differential)

Range Combo Box: Sets the channel range to sue for a channel's measurement

Ch 0-7 Combo Box: Sets the ground source for analog in channels 0 to 7

Ch 8-15 Combo Box: Sets the ground source for analog in channels 8 to 15

**Analog Output Group Box**

Enable All Channels Outputs Check Box: Sets all the analog output channels to enabled or disabled

Reset All Channels Button: Reset all the analog output channels to default settings

**Voltage Edit Box Fields (Channel 0 to Channel 7):** Enter output voltages for each of the analog output channels. Each channel's Voltage edit box has a set button to apply the new voltage settings.

## **Virtual Panel About Page**

|             | FPGA Board (0x108) ? ×                                                                                                                                     |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Setup I/O A | About                                                                                                                                                      |

|             | ExFpga - 3U PXI instrument driver for the GX3500 and<br>GX3700/GX3700e FLEX FPGA Boards<br>Version 2.2                                                     |

| Copyright @ | © 2009-2013, Marvin Test Solutions, Inc., All Rights Reserved.                                                                                             |

| Gx          | 3700 FLEX FPGA Board, FPGA-Version:0x0007<br>User FPGA Type: Stratix III EP3SL50F780<br>S/N: GX37000034-AL-AB-00<br>Expansion Board type: Programmable I/O |

|             | Upgrade Firmware                                                                                                                                           |

|             |                                                                                                                                                            |

|             |                                                                                                                                                            |

|             |                                                                                                                                                            |

|             |                                                                                                                                                            |

|             |                                                                                                                                                            |

|             |                                                                                                                                                            |

|             | nitialize Reset Apply Close Help                                                                                                                           |

Clicking on the About tab will show the About page as shown in Figure 2-7

Figure 2-14: GX3700 Virtual Panel – About Page

The top part of the **About** page displays version and copyright of the GX3700 driver. The bottom part displays the board summary, including the main board FPGA version, user FPGA part number, serial number, and each installed I/O Module FPGA version. The **About** page also contains a button **Upgrade Firmware...** used to upgrade the board FPGA. This button maybe used only when the board requires upgrade as directed by Marvin Test Solutions support. The upgrade requires a firmware file (.jam) that is written to the board FPGA. After the upgrade is complete you must shut down the computer to recycle power to the board.

#### 22 GX3700 User's Guide

# **Chapter 3 - Installation and Connections**

# **Getting Started**

This section includes general hardware installation procedures for the GX3700 board and installation instructions for the GX3700 (GXFPGA) software. Before proceeding, please refer to the appropriate chapter to become familiar with the board being installed.

| To Find Information on           | Refer to           |

|----------------------------------|--------------------|

| Hardware Installation            | This Chapter       |

| GX3700 Driver Installation       | This Chapter       |

| Programming                      | Chapter 4          |

| GXFPGA Design Tools and Tutorial | Chapter 5, 6 and 7 |

| Expansion Boards                 | Chapter 8          |

| GX3700 Function Reference        | Chapter 9          |

#### **Interfaces and Accessories**

The following accessories are available from Marvin Test Solutions for GX3700 switching board.

| Part / Model Number | Description                                           |

|---------------------|-------------------------------------------------------|

| GT95015             | Connector Interface SCSI to 100 Mil Grid Differential |

| GT95021             | 2' 68-Pin shielded cable                              |

| GT95022             | 3' 68-Pin shielded cable                              |

| GT95028             | 10' 68-Pin shielded cable                             |

| GT95031             | 6' 68-Pin shielded cable                              |

#### **Packing List**

All GX3700 boards have the same basic packing list, which includes:

- 1. GX3700 Board

- 2. GXFPGA Driver Disk

#### **Unpacking and Inspection**

After removing the board from the shipping carton:

- 1. Remove the board from the static bag by handling only the metal portions.

- 2. Be sure to check the contents of the shipping carton to verify that all of the items found in it match the packing list.

- 3. Inspect the board for possible damage. If there is any sign of damage, return the board immediately. Please refer to the warranty information at the beginning of the manual.

#### **System Requirements**

The GX3700 Instrument board is designed to run on PXI compatible computer running WindowsXP SP3-Windows 10 (32/64-bit).

The board requires one unoccupied 3U PXI bus slot.

### Installation of the GXFPGA Software

Before installing the board, it is recommended that you install the GXFPGA software as described in this section. To install the GXFPGA software, follow the instruction described below:

- 1. Insert the Marvin Test Solutions CD-ROM and locate the **GXFPGA.EXE** setup program. If your computer's Auto Run is configured, when inserting the CD, a browser will show several options. Select the Marvin Test Solutions Files option and then locate the setup file. If Auto Run is not configured, you can open the Windows explorer and locate the setup files (usually located under \Files\Setup folder). You can also download the file from Marvin Test Solutions' web site (www.marvintest.com).

- 2. Run the GXFPGA setup and follow the instruction on the Setup screen to install the GXFPGA driver.

**Note:** When installing under Windows, you may be required to restart the setup logging-in as a user with Administrator privileges. This is required in-order to upgrade your system with newer Windows components and to install kernel-mode device drivers (HW.SYS and HWDEVICE.SYS) which are required by the GXFPGA driver to access resources on your board.

- 3. The first setup screen to appear is the Welcome screen. Click Next to continue.

- 4. Enter the folder where GXFPGA is to be installed. Either click Browse to set up a new folder, or click Next to accept the default folder of C:\Program Files\Marvin Test Solutions\GXFPGA for 32-bit Windows or C:\Program Files (x86)\Marvin Test Solutions\GXFPGA for 64-bit Windows.

- 5. Select the type of Setup you wish and click **Next.** You can choose between **Typical**, **Run-Time** and **Custom** setups types. The **Typical** setup type installs all files. **Run-Time** setup type will install only the files required for controlling the board either from its driver or from its virtual panel. The **Custom** setup type lets you select from the available components.

The program will now start its installation. During the installation, Setup may upgrade some of the Windows shared components and files. The Setup may ask you to reboot after completion if some of the components it replaced were used by another application during the installation – do so before attempting to use the software.

You can now continue with the installation to install the board. After the board installation is complete you can test your installation by starting a panel program that lets you control the board interactively. The panel program can be started by selecting it from the Start, Programs, GXFPGA menu located in the Windows Taskbar.

# **Setup Maintenance Program**

You can run the Setup again after GXFPGA has been installed from the original disk or from the Windows Control Panel – Add Remove Programs applet. Setup will be in the Maintenance mode when running for the second time. The Maintenance window show below allows you to modify the current GXFPGA installation. The following options are available in Maintenance mode:

- Modify. When you want to add, or remove GXFPGA components.

- **Repair.** When you have corrupted files and need to reinstall.

- **Remove.** When you want to completely remove GXFPGA.

Select one of the options and click Next and follow the instruction on the screen until Setup is complete.

### **Overview of the GXFPGA Software**

Once the software is installed, the following tools and software components are available:

- **GXFPGA Panel** Configures and controls the GXFPGA board various features via an interactive user interface.

- **GXFPGA driver** A DLL based function library (GXFPGA.DLL, located in the Windows System folder) used to program and control the board. The driver uses Marvin Test Solutions' HW driver or VISA supplied by third party vendor to access and control the GXFPGA boards.

- **Programming files and examples** Interface files and libraries for support of various programming tools. A complete list of files and development tools supported by the driver is included in subsequent sections of this manual.

- Documentation On-Line help and User's Guide for the board, GXFPGA driver and panel.

- HW driver and PXI/PCI Explorer applet HW driver allows the GXFPGA driver to access and program the supported boards. The explorer applet configures the PXI chassis, controllers and devices. This is required for accurate identification of your PXI instruments later on when installed in your system. The applet configuration is saved to PXISYS.ini and PXIeSYS.ini and is used by instruments HW driver and VISA. The applet can be used to assign chassis numbers, Legacy Slot numbers and instrument alias names. The HW driver is installed and shared with all Marvin Test Solutions products to support accessing the PC resources. Similar to HW driver, VISA provides a standard way for instrument manufacturers and users to write and use instruments drivers. VISA is a standard maintained by the VXI Plug & Play System Alliance and the PXI Systems Alliance organizations (http://www.pxisa.org/). The VISA resource manager such as National Instruments Measurement & Automation (NI-MAX) displays and configures instruments and their address (similar to Marvin Test Solutions' PXI/PCI Explorer). The GXFPGA driver can work with either HW or VISA to control an access the supported boards.

#### **Installation Folders**

The GX3700 driver files are installed in the default folder C:\Program Files [(x86)]\Marvin Test Solutions\GXFPGA. You can change the default GXFPGA folder to one of your choosing at the time of installation.

| Name                          | Purpose / Contents                                                                                                                                                                               |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \Marvin Test Solutions\GXFPGA | The GXFPGA folder. Contains panel programs, programming libraries, interface files and examples, on-line help files and other documentation.                                                     |

| \Marvin Test Solutions\HW     | HW device driver. Provide access to your board hardware resources such<br>as memory, IO ports and PCI board configuration. See the<br>README.TXT located in this directory for more information. |

| \ATEasy\Drivers               | ATEasy drivers folder. GXFPGA Driver and example are copied to this directory only if ATEasy is installed to your machine.                                                                       |

| \Windows\System or System32   | Windows System directory. Contains the GXFPGA DLL,<br>GXFPGA64.DLL drivers, HW driver shared files and some upgraded<br>system components, such as the HTML help viewer, etc.                    |

During the installation, GXFPGA Setup creates and copies files to the following folders:

# Configuring Your PXI System using the PXI/PCI Explorer

To configure your PXI/PCI system using the **PXI/PCI Explorer** applet follow these steps:

- 1. **Start the PXI/PCI Explorer applet**. The applet can be start from the Windows Control Panel or from the Windows Start Menu, **Marvin Test Solutions**, **HW**, **PXI/PCI Explorer**.

- 2. **Identify Chassis and Controllers**. After the PXI/PCI Explorer is started, it will scan your system for changes and will display the current configuration. The PXI/PCI Explorer automatically detects systems that have Marvin Test Solutions controllers and chassis. In addition, the applet detects PXI-MXI-3/4 extenders in your system (manufactured by National Instruments). If your chassis is not shown in the explorer main window, use the Identify Chassis/Controller commands to identify your system. Chassis and Controller manufacturers should provide INI and driver files for their chassis and controllers which are used by these commands.

- 3. Change chassis numbers, PXI devices Legacy Slot numbering and PXI devices Alias names. These are optional steps and can be performed if you would like your chassis to have different numbers. Legacy slots numbers are used by older Marvin Test Solutions or VISA drivers. Alias names can provide a way to address a PXI device using a logical name (e.g. "FPGA1"). For more information regarding slot numbers and alias names, see the **GX3700Initialize** and **GxFpgaInitializeVisa** functions.

- 4. **Save your work**. PXI Explorer saves the configuration to the following files located in the Windows folder: PXISYS.ini, PXIeSYS.ini and GxPxiSys.ini. Click on the **Save** button to save your changes. The PXI/Explorer will prompt you to save the changes if changes were made or detected (an asterisk sign '\*' in the caption indicated changes).

| Ų.    |                                                                                                                                                                                                                                                                                                                                                                             | PXI/PCI Exp                                            | lorer                                             |                  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------|------------------|

| Slots | Status                                                                                                                                                                                                                                                                                                                                                                      |                                                        |                                                   |                  |

|       | <ul> <li>■ PXI System <external pc=""></external></li> <li>□ Chassis 1 <gx7000> <s <="" li=""> <li>□ A Slot 1 <system slot=""></system></li> <li>□ 3 Slot 3 - GX7400 Dual</li> <li>□ A VISA Resource =</li> <li>□ A NSlot = 0x103</li> <li>□ A Alias =</li> <li>□ Device Settings</li> <li>□ 9 Slot 9 - GX5961/4 Di</li> <li>□ 15 - GX2065 Dig</li> </s></gx7000></li></ul> | I-Output Progra<br>= PXI6::14::INS<br>gital I/O Timing | TR [Status=Device is w<br>/ Sync with Pin Electro | orking properly] |

| <     |                                                                                                                                                                                                                                                                                                                                                                             |                                                        |                                                   | >                |

|       | Display Options Reset 0                                                                                                                                                                                                                                                                                                                                                     | Chassis List                                           | Scan for New Devi                                 | ces Save         |

|       |                                                                                                                                                                                                                                                                                                                                                                             |                                                        |                                                   | Close            |

Figure 3-1: PXI/PCI Explorer

# **Board Installation**

#### Before you Begin

- Install the GXFPGA driver as described in the prior section.

- Configure your PXI/PC system using **PXI/PCI Explorer** as described in the prior section.

- Verify that all the components listed in the packing list (see previous section in this chapter) are present.

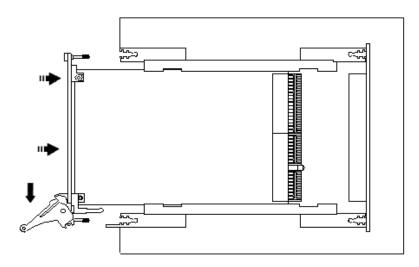

### **Electric Static Discharge (ESD) Precautions**

To reduce the risk of damage to the GX3700 board, the following precautions should be observed:

- Leave the board in the anti-static bags until installation requires removal. The anti-static bag protects the board from harmful static electricity.

- Save the anti-static bag in case the board is removed from the computer in the future.

- Carefully unpack and install the board. Do not drop or handle the board roughly.

- Handle the board by the edges. Avoid contact with any components on the circuit board.

**Caution** – Do not insert or remove any board while the computer is on. Turn off the power from the PXI chassis before installation.

#### **Installing a Board**

Install the board as follows:

- 1. Install first the GXFPGA Driver as described in the next section.

- 2. Turn off the PXI chassis and unplug the power cord.

- 3. Locate a PXI empty slot on the PXI chassis.

- 4. Place the module edges into the PXI chassis rails (top and bottom).

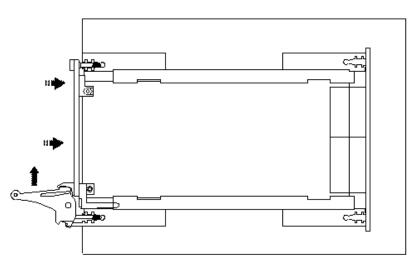

- 5. Carefully slide the PXI board to the rear of the chassis, make sure that the ejector handles are pushed <u>out</u> (as shown in Figure 3-2).

Figure 3-2: Ejector handles position during module insertion

6. After you feel resistance, push in the ejector handles as shown in Figure 3-3 to secure the module into the frame.

Figure 3-3: Ejector handles position after module insertion

- 7. Tighten the module's front panel to the chassis to secure the module in.

- 8. Connect any necessary cables to the board.

- 9. Plug the power cord in and turn on the PXI chassis.

#### **Plug & Play Driver Installation**

Plug & Play operating systems such as Windows notifies the user that a new board was found using the **New Hardware Found** wizard after restarting the system with the new board.

If another Marvin Test Solutions board software package was already installed, Windows will suggest using the driver information file: HW.INF. The file is located in your Program Files\Marvin Test Solutions\HW folder. Click **Next** to confirm and follow the instructions on the screen to complete the driver installation.

If the operating system was unable to find the driver (since the GXFPGA driver was not installed prior to the board installation), you may install the GXFPGA driver as described in the prior section, then click on the **Have Disk** button and browse to select the HW.INF file located in C:\Program Files [(x86)]\Marvin Test Solutions\HW.

If you are unable to locate the driver click **Cancel** to the found New Hardware wizard and exit the New Hardware Found Wizard, install the GXFPGA driver, reboot your computer and repeat this procedure.

The Windows Device Manager (open from the System applet from the Windows Control Panel) must display the proper board name before continuing to use the board software (no Yellow warning icon shown next to device). If the device is displayed with an error, you can select it and press delete and then press F5 to rescan the system again and to start the New Hardware Found wizard.

#### **Removing a Board**

Remove the board as follows:

- 1. Turn off the PXI chassis and unplug the power cord.

- 2. Locate a PXI slot on the PXI chassis.

- 3. Disconnect and remove any cables/connectors connected to the board.

- 4. Un-tighten the module's front panel screws to the chassis.

- 5. Push out the ejector handles and slide the PXI board away from the chassis.

- 6. Optionally uninstall the GXFPGA driver.

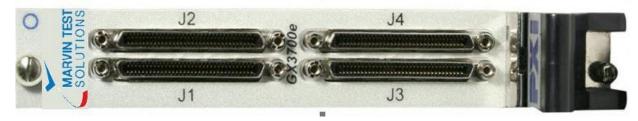

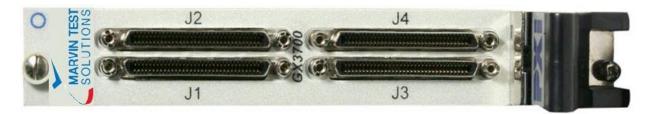

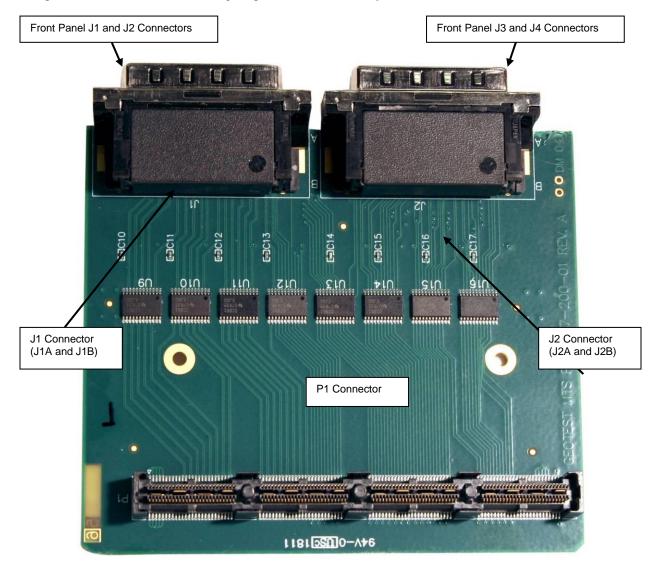

# **GX3701 Connectors**

These connectors exist only with the GX3701 daughter board card mounted on the GX3700/GX3700e.

| Connector | Description                                              |

|-----------|----------------------------------------------------------|

| J1        | FLEX I/O differential channels 1-32 or single ended 1-64 |

| J2        | FLEX I/O channels 33-64                                  |

| J3        | FLEX I/O channels 65-96                                  |

| J4        | FLEX I/O channels 97-128                                 |

#### Table 3-1: GX3701 Connectors

Figure 3-4: GX3701e Connectors J1-J4

Figure 3-5: GX3701 Connectors J1-J4

Connections to the GX3700/GX3701 may be made with 68-pin VHDCI male plug connector. Shielded cables with matching connectors are available from Marvin Test Solutions.

The following section describes J1-J4 connectors.

| Pin | Function           | Pin | Function     | Pin | Function           | Pin | Function     |

|-----|--------------------|-----|--------------|-----|--------------------|-----|--------------|

| 1   | Flex I/O 1P        | 18  | Flex I/O 18P | 35  | Flex I/O 1N        | 52  | Flex I/O 18N |

| 2   | Flex I/O 2P        | 19  | Flex I/O 19P | 36  | Flex I/O 2N        | 53  | Flex I/O 19N |

| 3   | Flex I/O 3P        | 20  | Flex I/O 20P | 37  | Flex I/O 3N        | 54  | Flex I/O 20N |

| 4   | Flex I/O 4P        | 21  | Flex I/O 21P | 38  | Flex I/O 4N        | 55  | Flex I/O 21N |

| 5   | Flex I/O 5P        | 22  | Flex I/O 22P | 39  | Flex I/O 5N        | 56  | Flex I/O 22N |

| 6   | Flex I/O 6P        | 23  | Flex I/O 23P | 40  | Flex I/O 6N        | 57  | Flex I/O 23N |

| 7   | Flex I/O 7P        | 24  | Flex I/O 24P | 41  | Flex I/O 7N        | 58  | Flex I/O 24N |

| 8   | Flex I/O 8P        | 25  | Flex I/O 25P | 42  | Flex I/O 8N        | 59  | Flex I/O 25N |

| 9   | Flex I/O 9P        | 26  | Flex I/O 26P | 43  | Flex I/O 9N        | 60  | Flex I/O 26N |

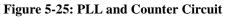

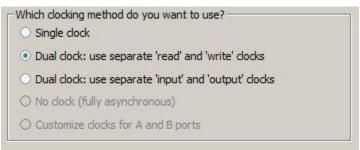

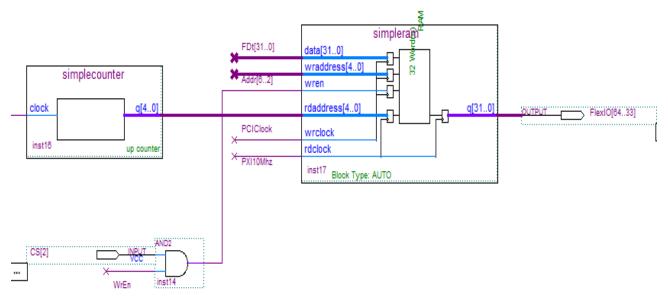

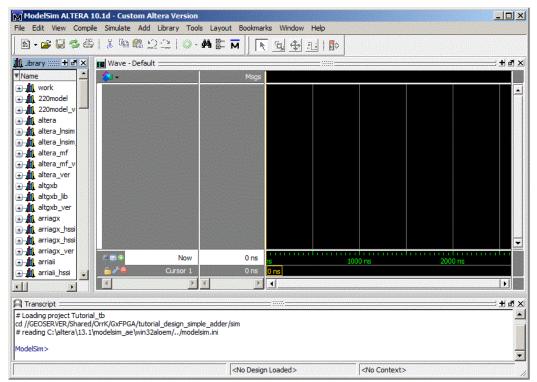

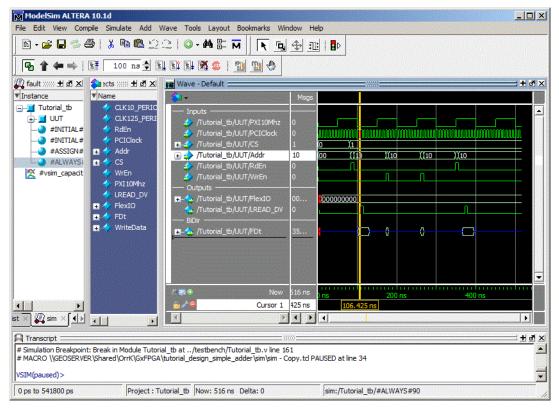

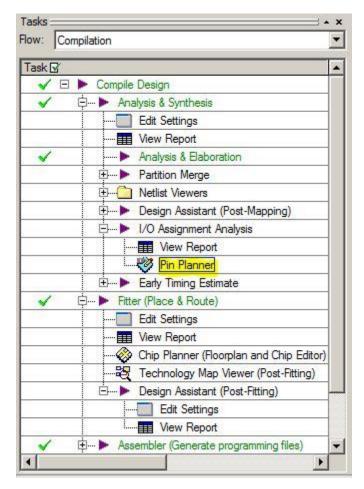

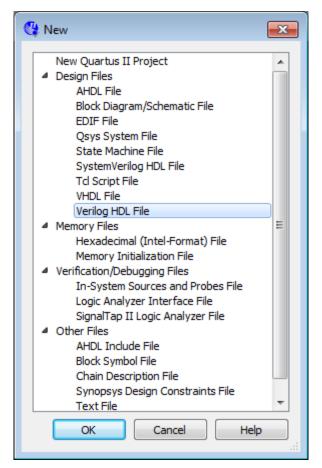

| 10  | Flex I/O 10P       | 27  | Flex I/O 27P | 44  | Flex I/O 10N       | 61  | Flex I/O 27N |