# GX5961, GX5964/GX5964A Digital I/O PXI Boards

# **User's Guide**

Last Updated November 23, 2016

# Safety and Handling

Each product shipped by Marvin Test Solutions is carefully inspected and tested prior to shipping. The shipping box provides protection during shipment, and can be used for storage of both the hardware and the software when they are not in use.

The circuit boards are extremely delicate and require care in handling and installation. Do not remove the boards from their protective plastic coverings or from the shipping box until you are ready to install the boards into your computer.

If a board is removed from the computer for any reason, be sure to store it in its original shipping box. Do not store boards on top of workbenches or other areas where they might be susceptible to damage or exposure to strong electromagnetic or electrostatic fields. Store circuit boards in protective anti-electrostatic wrapping and away from electromagnetic fields.

Be sure to make a single copy of the software CD for installation. Store the original CD in a safe place away from electromagnetic or electrostatic fields. Return compact disks (CD) to their protective case or sleeve and store in the original shipping box or other suitable location.

# Warranty

Marvin Test Solutions products are warranted against defects in materials and workmanship for a period of 12 months. Marvin Test Solutions shall repair or replace (at its discretion) any defective product during the stated warranty period. The software warranty includes any revisions or new versions released during the warranty period. Revisions and new versions may be covered by a software support agreement. If you need to return a board, please contact Marvin Test Solutions Customer Technical Services Department via <a href="http://www.marvintest.com/magic/">http://www.marvintest.com/magic/</a> - the Marvin Test Solutions on-line support system.

# If You Need Help

Visit our web site at <u>http://www.marvintest.com</u> more information about Marvin Test Solutions products, services and support options. Our web site contains sections describing support options and application notes, as well as a download area for downloading patches, example, patches and new or revised instrument drivers. To submit a support issue including suggestion, bug report or questions please use the following link: <a href="http://www.marvintest.com/magic/">http://www.marvintest.com/magic/</a>

You can also use Marvin Test Solutions technical support phone line (949) 263-2222. This service is available between 8:30 AM and 5:30 PM Pacific Standard Time.

### Disclaimer

In no event shall Marvin Test Solutions or any of its representatives be liable for any consequential damages whatsoever (including unlimited damages for loss of business profits, business interruption, loss of business information, or any other losses) arising out of the use of or inability to use this product, even if Marvin Test Solutions has been advised of the possibility for such damages.

# Copyright

Copyright © 2010-2016 by Marvin Test Solutions, Inc. All rights reserved. No part of this document can be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Marvin Test Solutions.

# Trademarks

| ATEasy®, CalEasy, DIOEasy®, DtifEasy, WaveEasy                                          | Marvin Test Solutions, Inc.,<br>Geotest – Marvin Test<br>Systems, Inc (prior company<br>name) |

|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| C++ Builder, Delphi                                                                     | Embarcadero Technologies<br>Inc.                                                              |

| LabView, LabWindowstm/CVI                                                               | National Instruments                                                                          |

| Microsoft Developer Studio, Microsoft Visual C++, Microsoft Visual Basic, .NET, Windows | Microsoft Corporation                                                                         |

All other trademarks are the property of their respective owners.

# **Table of Contents**

| Safety and Handling                       | i  |

|-------------------------------------------|----|

| Warranty                                  | i  |

| If You Need Help                          | i  |

| Disclaimer                                | i  |

| Copyright                                 | i  |

| Trademarks                                | ii |

| Chapter 1 - Introduction                  | 7  |

| Manual Scope and Organization             | 7  |

| Manual Scope                              | 7  |

| Manual Organization                       | 7  |

| Conventions Used in this Manual           | 7  |

| Chapter 2 - Overview                      | 9  |

| Introduction                              | 9  |

| Features                                  | 9  |

| PXI Compatibility                         |    |

| Software                                  |    |

| Applications                              |    |

| Boards Description                        |    |

| GX5960 Models and Accessories             | 14 |

| GX5961/GX5964/ GX5964A Specifications     |    |

| Timing                                    |    |

| Drive / Sense Modes and Channel I/O       | 16 |

| I/O Connections                           |    |

| Analog Measurement Bus                    |    |

| Parametric Measurement Unit (PMU)         |    |

| Environmental                             |    |

| Physical Characteristics                  |    |

| GX5961 Timing / Sync Board Specifications |    |

| External Timing, Control & Status Signals |    |

| Chapter 3 - Installation and Connections  |    |

| Getting Started                           | 21 |

| Interfaces and Accessories                |    |

| Packing List                              |    |

| Unpacking and Inspection                  |    |

| System Requirements                       |    |

| Installation of the GtDio6X Software                   |  |

|--------------------------------------------------------|--|

| Setup Maintenance Program                              |  |

| Overview of the GtDio6x Software                       |  |

| Installation Folders                                   |  |

| Configuring Your PXI System using the PXI/PCI Explorer |  |

| Board Installation                                     |  |

| Before you Begin                                       |  |

| Electric Static Discharge (ESD) Precautions            |  |

| Chassis Requirements                                   |  |

| Board Installation in a GX70x5 PXI Chassis             |  |

| Installing a Board                                     |  |

| Plug & Play Driver Installation                        |  |

| Removing a Board                                       |  |

| Connectors and Jumpers                                 |  |

| GX5691 Connectors                                      |  |

| GX5694 Rev B Connectors                                |  |

| GX5694A Connectors                                     |  |

| GX5961 J7- Front Panel Power Connector                 |  |

| GX5961 J6- Front Panel Analog I/O Connector            |  |

| GX5961 J8- Front Panel I/O Connector                   |  |

| GX5961 J9- Front Panel Auxiliary Channels Connector    |  |

| GX5961 J10- Front Panel High Voltage Connector         |  |

| GX5964/GX5964A J7- Front Panel Power Connector         |  |

| GX5964 J6- Front Panel Analog I/O Connector            |  |

| GX5964 J8- Front Panel I/O Connector                   |  |

| GX5964A P3, P2 - Front Panel I/O Connector             |  |

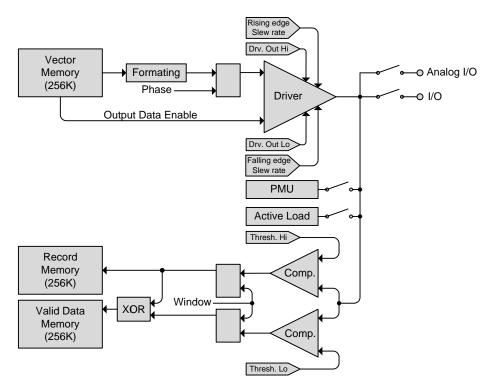

| Chapter 4 - Theory of Operation                        |  |

| Overview                                               |  |

| Architecture                                           |  |

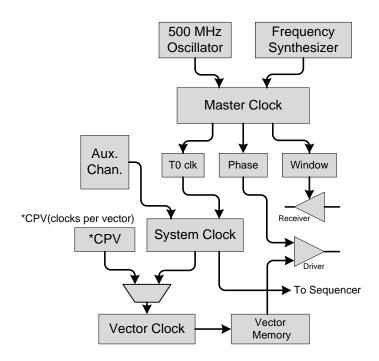

| Master Clock                                           |  |

| Timing Generator                                       |  |

| Step Memory and Sequencer Engine                       |  |

| Vector Memory                                          |  |

| Record Memory                                          |  |

| Test Logic                                             |  |

| Aux I/O                                                |  |

| I/O Channels                                           |  |

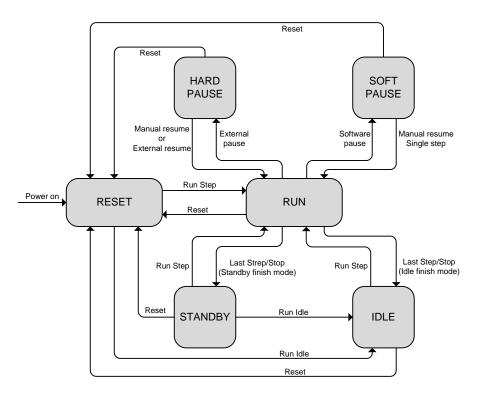

| Sequencer                                          |    |

|----------------------------------------------------|----|

| Reset State                                        |    |

| Idle State                                         |    |

| Standby State                                      |    |

| Run State                                          |    |

| Soft Pause State                                   |    |

| Hard Pause State                                   |    |

| Finish/Idle State                                  |    |

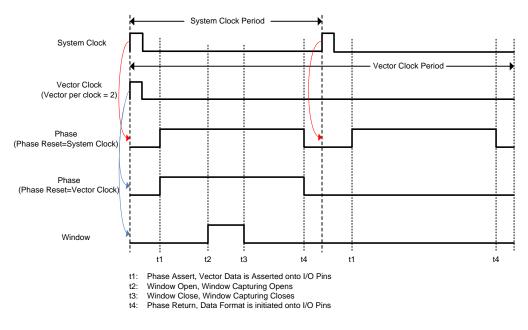

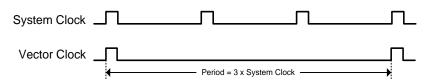

| Clocks                                             |    |

| Master Clock                                       |    |

| System Clock                                       |    |

| Vector Clock                                       |    |

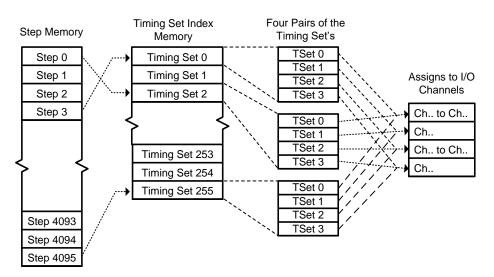

| Timing Sets                                        |    |

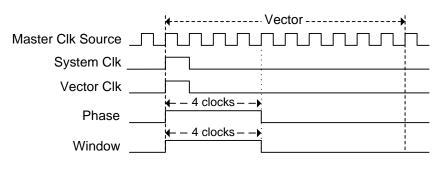

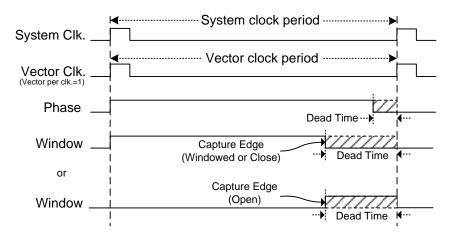

| Phase                                              |    |

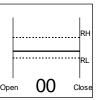

| Window                                             |    |

| Indexed Timing Mode                                |    |

| Vector Memory                                      |    |

| Vector Assignment                                  |    |

| T0 Clock                                           |    |

| Timing                                             |    |

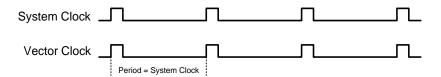

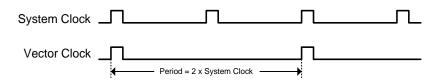

| Clocks per Vector                                  |    |

| Record Mode                                        |    |

| Phase Reset Source                                 |    |

| Last Step Flag                                     |    |

| Control Logic                                      |    |

| Record Memory                                      |    |

| Test Logic                                         |    |

| Control Resource                                   |    |

| Triggers                                           |    |

| Channel Test                                       |    |

| I/O Channel Operation                              |    |

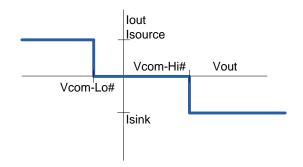

| Programmable Input Current Load and Voltage Clamps | 61 |

| Programmable Resistive Load                        |    |

| Input Threshold Voltages                           |    |

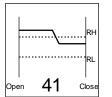

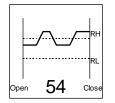

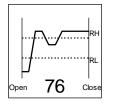

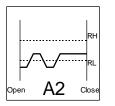

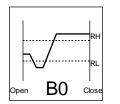

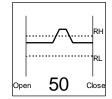

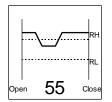

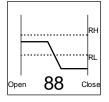

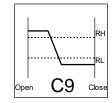

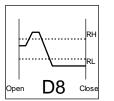

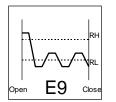

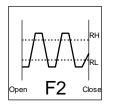

| Output Data Formatting                             |    |

| Output Slew Rate                                   |    |

| PMU Functionality                                  |    |

#### vi GX5961/GX5964 User's Guide

| Probe | 64 |

|-------|----|

| ndex  | 67 |

# **Chapter 1 - Introduction**

# Manual Scope and Organization

#### Manual Scope

The purpose of this manual is to provide all the necessary information to install, use, and maintain the GX5961/GX5964 (referred in this manual as GX5960) digital subsystem. This manual assumes the reader has a general knowledge of PC based computers, Windows operating systems, and some understanding of digital I/O.

Refer to the GtDio6x for more information regarding the GtDio6x software including driver functions, programming examples, virtual panel and more.

#### **Manual Organization**

The GX6961/4 manual is organized in the following manner:

| Chapter                                    | Content                                                                                                                                                |  |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Chapter 1 -<br>Introduction                | Introduces the this manual. Lists all the supported GX5960 boards and shows warning conventions used in the manual.                                    |  |

| Chapter 2 – Overview                       | Describes the GX5960 series features, board description, architecture, specifications.                                                                 |  |

| Chapter 3 –Installation<br>and Connections | Provides instructions on how to install a GX5960 boards and the GtDio6x software.                                                                      |  |

| Chapter 4 – Theory of Operation            | Presents the theory of operation for the GX5960 boards, with an overview of operation and a simple description of operation for one channel (I/O pin). |  |

# **Conventions Used in this Manual**

| Symbol Convention | Meaning                                                                             |  |

|-------------------|-------------------------------------------------------------------------------------|--|

| <b>\</b>          | Static Sensitive Electronic Devices. Handle Carefully.                              |  |

| STOP              | Warnings that may pose a personal danger to your health. For example, shock hazard. |  |

|                   | Cautions where computer components may be damaged if not handled carefully.         |  |

| TIP               | Tips that aid you in your work.                                                     |  |

| Formatting<br>Convention | Meaning                                                                                                                 |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Monospaced Text          | Examples of field syntax and programming samples.                                                                       |

| Bold type                | Words or characters you type as the manual instructs. For example: function or panel names.                             |

| Italic type              | Specialized terms. Titles of other reference books. Placeholders for items you must supply, such as function parameters |

8 GX5961/GX5964 User's Guide

# **Chapter 2 - Overview**

# Introduction

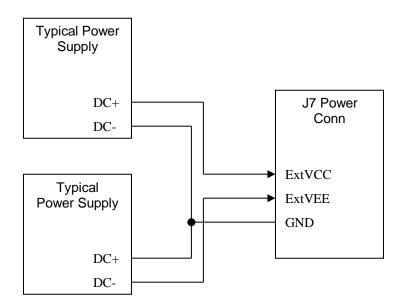

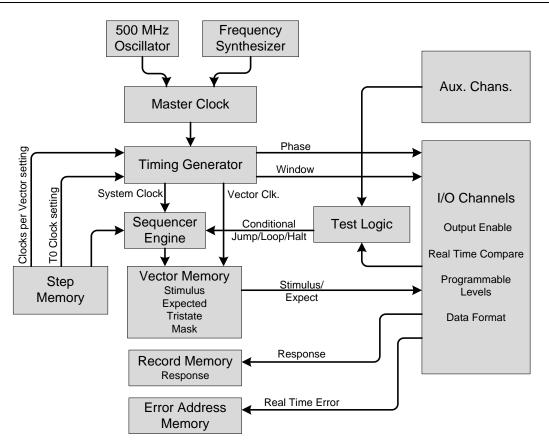

The GX5960 digital subsystem represents the highest level of performance available for PXI-based digital instrumentation. The GX5960 series includes two types of cards: GX5961 and GX5964/GX5964A. Based on the proven architecture of the Marvin Test Solutions' PXI GX5055 and the EADS VXI T964 boards, the GX5960 series offers high performance pin electronics and a timing generator / sequencer in a compact, 6U PXI form factor. The GX5960 digital subsystem consists of one GX5961 Clock/ Trigger board with 16 driver / sensor channels and the GX5964 driver / sensor board, which supports 32 bi-directional I/O channels. Up to 528 digital I/O channels can be supported by the GX5960 digital subsystem. Each digital channel features a wide drive / sense voltage range of -15 V to +25V (maximum swing of 26 volts) which can be individually programmed for a drive hi, drive lo, sense hi, sense lo, and a load value (with commutation voltage level) – offering the user complete flexibility when creating test programs and fixtures for multiple types of UUTs. In addition, each channel offers a parametric measurement unit (PMU) for DC measurements.

# Features

The GX5960 digital subsystem offers real-time digital stimulus, record, or expect data modes on all I/O channels and 32 high voltage utility I/O signals. Vector memory depth is 256K words. Each channel can be configured as an input or output on a per cycle basis. Six drive data formats are supported: NR, R1, R0, RZ, RC, and Complement Surround – providing flexibility to create a variety of bus cycles and waveforms to test board and box level products.

The GX5961 provides timing, input / output synchronization signals, and sequencing as well as 16 I/O channels. Additional channels can be added to the system by installing one or more, GX5964 boards which are interconnected via the PXI local and trigger busses. The GX5961 offers a flexible clock system which allows the module to operate as a timing master to the UUT or be slaved to the UUT's time base or some other external clock. All pin electronic resources are independent on a per channel basis – offering the user complete flexibility when programming drive / sense levels, source / sink currents, slew rate, skew, or PMU functions. The PMU can operate in the force voltage / measure current or force current / measure voltage mode and is useful for measuring a UUT's DC characteristics. In addition, each I/O channel includes an analog bus relay, which allows each channel to support hybrid channel (digital or analog) measurement capabilities. For analog stimulus / response measurements, the analog bus can be connected to external resources via a dedicated analog bus connector located on the front panel of the module.

The following provides a summary of the GX5960 series' main features:

- Cycle based, 50 MHz dynamic digital subsystem with high performance timing generator

- High voltage pin electronics with per channel programmability

- Per channel parametric measurement unit (PMU)

- Analog bus access for each I/O channel

- Dual level drive / sense, and programmable load on a per channel basis

- 256 timing sets with 4 phases and 4 windows, alternate configurations include 1K and 4K timing sets

- 0 64 us phase and window programming range with 1ns resolution

- Supports up to 528 bi-directional I/O channels

- 256K of vector memory

- Comprehensive software tool set supports CASS legacy programs and importing of IEEE 1445 compliant vector files

- 6U PXI Instrument

# **PXI Compatibility**

The GX5960 subsystem can operate in any 6U PXI chassis that supports an air flow rate of 20 cfm/slot. Power for the pin electronics requires the use of external power supplies or the GX5960 subsystem can be used with a Marvin Test Solutions GX7005A / GX7015A PXI chassis which is designed specifically for high performance / high power digital applications and includes the necessary pin electronics power supplies as well as a high capacity cooling system.

# Software

The GX5960 series is supplied with the GtDio6x software package that includes vector editing, a virtual instrument panel, and 32/64-bit DLL driver libraries and documentation. The virtual panel can be used to interactively program and control the instrument from a window that displays the instrument's current settings and status. In addition, interface files are provided to support access to programming tools and languages such as ATEasy, LabView, Microsoft® and Borland® C/C++, Microsoft Visual Basic®, Borland Delphi, and Pascal. On-Line help file and PDF User's Guide provides documentation that includes instructions for installing, using and programming the board.

Other optional software packages are available to support the importing of legacy digital test programs, CASS digital TPS'a or IEEE-1445 .tap files.

Refer to the GtDio6x for more information regarding the GtDio6x software including driver functions, programming examples, virtual panel and more.

# **Applications**

The GX5960 digital subsystem can be used to support a variety of digital test applications including:

- Automatic Test Equipment (ATE)

- High-speed functional digital test

- Vector capture

- Hybrid and digital device test

- Memory testing

- LRU and SRU test

# **Boards Description**

The GX5961 has 5 connectors on the front (Power, IO, Analog I/O, High Voltage and Auxiliary) and 3 PXI on the back.

Figure 2-1: GX5961 Board

The GX5964 has 3 connectors (Power, I/O and Analog I/O) on the front and 3 PXI on the back

Figure 2-2: GX5964 Board

The GX5964A has 4 connectors (Power, 2 I/O and Analog I/O) on the front and 3 PXI on the back

Figure 2-3: GX5964A Board

# **GX5960 Models and Accessories**

| Model / Accessory                                                                                                      | Description                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| GX5964/ GX5964A, DIO board                                                                                             | Digital input/output and domain timing and control.                                                                   |

| GX5961, Timing / Synch board                                                                                           | Timing and synchronization board. Includes 16 digital I/O channels, 4 aux I/O channels, 32 HV open collector channels |

| GT97110, DB9, sub D, 3' female power connector cable                                                                   | Supplies external power (Vcc ⋁) to the GX5964 and GX5961                                                              |

| GT95014, Connector Interface for the GX5960,<br>SCSI to 100 Mil Grid, Single Ended                                     | UUT I/O Interface, Analog Bus, Aux channels, HV I/O                                                                   |

| GT95015, Connector Interface for the GX5960,<br>SCSI to 100 Mil Grid, Differential                                     | UUT I/O Interface, Analog Bus, Aux channels, HV I/O                                                                   |

| GT95015- SCSI, Connector Interface for the<br>GX5960, SCSI to 100 Mil Grid, Differential, no J2<br>connector installed | UUT I/O Interface, Analog Bus, Aux channels, HV I/O                                                                   |

| Connector I/F for GX5960, SCSI to 100 Mil Grid,<br>Single Ended (both 64 & 14 pin)                                     | UUT I/O Interface, Analog Bus, Aux channels, HV I/O                                                                   |

| GT95021, 2' shielded cable for GX5960 (68 Pin)                                                                         | UUT I/O Interface (GX5964/GX5961 only), Analog Bus,<br>Aux channels, HV I/O                                           |

| GT95022, 3' shielded cable for GX5960 (68 Pin)                                                                         | UUT I/O Interface (GX5964/GX5961 only), Analog Bus,<br>Aux channels, HV I/O                                           |

| GT95031, 6' shielded cable for GX5960 (68 Pin)                                                                         | UUT I/O Interface (GX5964/GX5961 only), Analog Bus,<br>Aux channels, HV I/O                                           |

| GT95028,10' shielded cable for GX5960 (68 Pin)                                                                         | UUT I/O Interface (GX5964/GX5961 only), Analog Bus,<br>Aux channels, HV I/O                                           |

| GX95917, 20' 16-Channels DIO Shielded Flat Cable<br>Assy                                                               | UUT I/O Interface P2/P3 front connectors (GX5964A only)                                                               |

| GX95918, 20' 36-Channels DIO Shielded Flat Cable<br>Assy                                                               | UUT I/O Interface P2/P3 front connectors (GX5964A only)                                                               |

# GX5961/GX5964/ GX5964A Specifications

The following table outlines the specifications of the GX5961/GX5964/GX5964A boards.

# Timing

| Internal Test Clock or System Clock (T0 Clock)                         | 15.625 KHz to 50 MHz (using the 500 MHz master clock)                                                                                                                                     |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Test Clock Time base                                                   | Ext Reference Clock: 1 MHz to 80 MHz<br>Internal reference clock: 20 MHz                                                                                                                  |

| T0_CLK Timing Resolution                                               | 1 ns (using the 500 MHz master clock)                                                                                                                                                     |

| Master Clock (Phase and Window Timing Source)                          | 500 MHz (internal oscillator), +/- 50 ppm<br>40 MHz to 500 MHz (PLL), +/- 50 ppm                                                                                                          |

| Master Clock Reference                                                 | Internal: 20 MHz<br>PXI Clock 10 MHz<br>Front panel: 5 MHz to 80 MHz                                                                                                                      |

| Timing Set Options                                                     | Index Mode: 256 Timing Set groups with 4 Phases, 4 Windows, and 4K sequence steps.                                                                                                        |

| Phase Programming Range (Assert / Return)                              | 0 ns to 64 us (using the 500 MHz master clock)                                                                                                                                            |

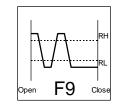

| Window Programming Range (Open / Close)                                | 0 ns to 64 us (using the 500 MHz master clock)                                                                                                                                            |

| Phase and Window Timing Resolution                                     | 1 ns, using the 500 MHz master clock                                                                                                                                                      |

| Minimum Phase / Window Pulse Width; Assert /<br>Return or Open / Close | 8 ns, using the 500 MHz master clock                                                                                                                                                      |

| Phase / Window Reference                                               | Phase: System or Vector Clock (selectable per Seq<br>Step)<br>Window: Vector clock only                                                                                                   |

| Phase / Window Dead Time                                               | 10 ns at end of the Vector period (using 500 MHz master clock)                                                                                                                            |

| Clocks per vector                                                      | 1 to 256 (selectable per Sequencer Step)                                                                                                                                                  |

| Pause / Vector Clutch                                                  | Phase and Window are frozen when Pause is asserted<br>Pause on external event<br>Pause based on phase edge<br>Resume after programmed delay<br>Resume on an external signal or CPU resume |

| Halt / System Clutch                                                   | Halt based on an external signal<br>Halt on error<br>Halt on a Sync pulse (used as a breakpoint)                                                                                          |

| Pause / Pattern and Halt / System Clutch Sources                       | PXI trigger lines<br>Aux I/O 1-12<br>Ch. 1-32 (with mask/expect) , (GX5964/GX5964A)<br>Ch. 1-16 (with mask / expect), (GX5961)<br>Phase 1-4 (for Pause)                                   |

# Drive / Sense Modes and Channel I/O

Note: All specifications based on pin electronic rails (VCC & VEE) of +18 V and -14 V) unless noted otherwise.

| Number of I/O Channels                                   | 16 per card (GX5961)<br>32 per card (GX5964/GX5964A)                                                                                                                                                 |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog bus                                               | <ul> <li>32 relay controlled connections to I/O pin<br/>(GX5964/GX5964A)</li> <li>16 relay controlled connections to I/O pin (GX5961)</li> <li>Individual control for each channel</li> </ul>        |

| Test Modes                                               | Dynamic or Static                                                                                                                                                                                    |

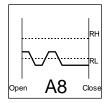

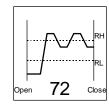

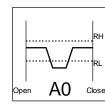

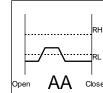

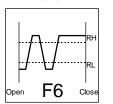

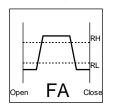

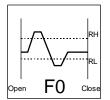

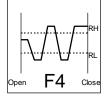

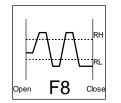

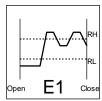

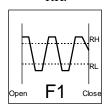

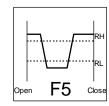

| Data Output Formats<br>(per channel)                     | Drive Hi, Drive Lo, Hi-Z<br>Formatted Data: No return, Return to 1, Return to 0,<br>Return to Hi-Z, Return to complement, Surround by<br>complement; selectable on a per channel basis               |

| Drive Data Timing (per channel)                          | Data assert / de-assert based on Phases 1-4                                                                                                                                                          |

| Capture modes<br>(per channel)                           | Mask<br>Opening edge of Window<br>Closing edge of Window<br>Window – data is valid for entire window duration                                                                                        |

| Drive / expect mode                                      | Output: Drive High, Drive Low, Hi-Z<br>Expect: 1, 0, OK, between states, or mask<br>Keep last<br>Toggle last<br>Accumulate CRC-16                                                                    |

| Recording modes<br>(per sequence step)                   | Record errors for programmable inputs that have Good 1<br>& Good 0<br>Record errors for inputs that have only a Good 1<br>Record raw data based on NOT a Good 0<br>Record raw data based on a Good 1 |

| Error address record                                     | Record address for memory errors<br>1K deep error memory                                                                                                                                             |

| Number of Drive and Sense Voltage References             | GX5961:<br>16 Drive Hi / Drive Lo<br>16 Sense Hi / Sense Lo<br>GX5964/GX5964A:<br>32 Drive High / Drive Low<br>32 Sense High / Sense Low                                                             |

| Drive Voltage Level (for specified Vee and Vcc voltages) | Drive High: -9 to +15V<br>Drive Low: -10 to + 11V                                                                                                                                                    |

| Drive High Range                       | Vee $+5V$ to Vcc $-3$                                                                                                               |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Drive Low Range                        | Vee $+4V$ to Vcc $-7V$                                                                                                              |

| Maximum Drive High and Low Level Range | -14V to +26V                                                                                                                        |

| Drive High and Low Voltage Level Range | Min: 0.5 V p-p<br>Max: 26 V p-p                                                                                                     |

| Drive High and Low Voltage Accuracy    | +/- 50 mv, < 26 V p-p drive voltage                                                                                                 |

| Drive High and Low Voltage Resolution  | 16 bits                                                                                                                             |

| Output Impedance                       | 12 or 50 ohms, typical                                                                                                              |

| Drive Current                          | 200 mA max per channel<br>1.6 A per board, max (GX5964/GX5964A)<br>0.8 A per board, max (GX5961)                                    |

| Short Circuit Protection               | Programmable current level with automatic disable, per channel basis                                                                |

| Slew Rate                              | 0.1 to 1 V/ns, adjustable, programmable on a per channel basis                                                                      |

| Channel Skew                           | 320 ps, typical<br>500 ps max., after calibration, for all channels<br>(Drive and sense)                                            |

| Channel De-Skew                        | Range: +/- 5 ns<br>Resolution: 312.5 ps<br>- Programmable on a per channel basis.<br>- Separate deskew control for drive and sense. |

| Sense Voltage Range                    | Sense High: -10 to +11 V<br>Sense Low: -10 to +11 V                                                                                 |

| Sense Range Relative to Voltage Rails  | Vee $+2V$ to Vcc $-7V$                                                                                                              |

| Maximum Sense Range                    | -16V to +22V                                                                                                                        |

| Sense Voltage Accuracy                 | +/- 50 mv, < 26 V p-p sense voltage                                                                                                 |

| Sense Voltage Resolution               | 16 bits                                                                                                                             |

| Input Leakage Current                  | 50 nA, max                                                                                                                          |

| Pull-Up / Pull-Down Current Source/ Sink             | Current Source: 24 ma, programmable on a per channel<br>basis<br>Current Sink: -24 ma, programmable on a per channel<br>basis<br>V commutate: -10 to +11 V., programmable on a per<br>channel basis |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pull-Up / Pull-Down Current Source / Sink Accuracy   | 240 uA                                                                                                                                                                                              |

| Pull-Up / Pull-Down Current Source / Sink Resolution | 16 bits                                                                                                                                                                                             |

| Voltage Commutation Range                            | Vee +2V to Vcc - 7V                                                                                                                                                                                 |

| Voltage Commutation Accuracy                         | +/- 50 mv, < 25 V range                                                                                                                                                                             |

| Voltage Commutation Resolution                       | 16 bits                                                                                                                                                                                             |

| Resistive Load                                       | Range: Hi-Z, 250 ohm, 1 K ohm, programmable on a per channel basis                                                                                                                                  |

| Memory                                               | 256K words                                                                                                                                                                                          |

# I/O Connections

| Analog Bus (For Connections to Analog<br>Instrumentation) | GX5964: 68 position SCSI III Type<br>GX5964A: 2 Shielded Flat Cables 16-channels each                                              |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| I/O, External Control, Timing                             | 68 position SCSI III Type                                                                                                          |

| Vcc range                                                 | +10V to +29V                                                                                                                       |

| Vee range                                                 | -18V to -3V                                                                                                                        |

| Vcc - Vee range                                           | +13V (min) to +32 V (max)                                                                                                          |

| External Vcc / Vee                                        | 15 position D-sub, male<br>+18 volts @ 6 A (GX5964/GX5964A)<br>@3 A (GX5961)<br>-14 volts @ 6 A (GX5964/GX5964A)<br>@ 3 A (GX5961) |

# Analog Measurement Bus

| Number Of Analog I/O Channels | 16 per card (GX5961)<br>32 per card (GX5964/GX5964A)                                                          |

|-------------------------------|---------------------------------------------------------------------------------------------------------------|

| Control                       | Independent connect / disconnect to each I/O channel,<br>Independent disconnect relay to each digital channel |

| Switching Current             | Maximum current: 0.5 A per channel                                                                            |

| Operating Voltage             | 30 volts, max                                                                                                 |

# Parametric Measurement Unit (PMU)

| Number Of Parametric Measurement Units                             | 32, one per channel (GX5964/GX5964A)<br>16, one per channel (GX5961) |

|--------------------------------------------------------------------|----------------------------------------------------------------------|

| Modes                                                              | Force voltage, measure current<br>Force current, measure voltage     |

| Force Voltage Range (for specified Vcc and Vee operating voltages) | -10 volts to + 15 volts                                              |

| Maximum Force Voltage Range                                        | Vee $+4V$ to Vcc $-3V$                                               |

| Force Voltage Accuracy                                             | +/- 50 mV, 25 volt range                                             |

| Force Voltage & Current Resolution                                 | 16 bits                                                              |

| Force Current Range                                                | +/- 25 mA FS<br>+/- 200 mA FS                                        |

| Force Current Accuracy                                             | +/- 50 uA, 25 mA range<br>+/- 2 mA, 200 mA range                     |

| Measure Voltage Range                                              | -13 to +15 volts                                                     |

| Maximum Measure Voltage Range                                      | Vee $+1V$ to Vcc $-3V$                                               |

| Measure Voltage & Current Resolution                               | 16 bits                                                              |

| Measure Voltage Accuracy                                           | +/- 50 mV, -9 to +13 volt range                                      |

| Measure Current Range                                              | +/- 25 ma FS<br>+/- 200 ma FS                                        |

| Measure Current Accuracy                                           | +/- 50 uA, (25 mA range)<br>+/- 2 mA (200 mA range)                  |

#### Environmental

| Operating Temperature | 0 to 50° C           |

|-----------------------|----------------------|

| Storage Temperature   | -20° C to 70° C      |

| Vibration             | 5 g at 500 Hz        |

| Shock                 | 10 g for 6 ms ½ sine |

# **Physical Characteristics**

| Size   | 6U PXI, single slot |

|--------|---------------------|

| Weight | 1.2 lbs (544 g)     |

Note: Specifications subject to change without notice.

# **GX5961 Timing / Sync Board Specifications**

#### **External Timing, Control & Status Signals**

| Sync outputs                    | 2, Start of Sequence; Start of Sequence Step                                                                                                                                                                                                                                                                                                         |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General purpose aux I/O         | <ul><li>12 channels</li><li>64 output selections for selected internal signals.</li><li>7 input selected signals</li></ul>                                                                                                                                                                                                                           |

| Input aux I/O selections        | Synthesizer reference clock, System clock, Break (System Clutch), Halt (Vector Clutch), Sequence Jump signals                                                                                                                                                                                                                                        |

| Output auxiliary I/O selections | Phase, Window, Waveform, Syncs, Seq flag, Seq Active, Seq Idle, T0_Clock, Pat_Clock, misc test signals.                                                                                                                                                                                                                                              |

| Probe                           | Ground, Probe Button, Probe LED, Monitor                                                                                                                                                                                                                                                                                                             |

| High Voltage I/O                | Channels: 32<br>Output characteristics:<br>Configuration: open collector<br>Maximum output voltage: 28 VDC<br>Maximum current: 1 A per byte<br>Passive pull-up: 1 KOhm to 4.5 volts<br>OV shutdown: 28 VDC to 36 VDC<br>Input characteristics:<br>Threshold range: 0V to 10.235V<br>Threshold resolution: 5 mV<br>Threshold accuracy: +/- 35 mV + 1% |

Note: Specifications subject to change without notice.

# **Chapter 3 - Installation and Connections**

# **Getting Started**

This section includes general hardware installation procedures for the GtDio6x board and installation instructions for the GtDio6x software. Before proceeding, please refer to the appropriate chapter to become familiar with the board being installed.

| To Find Information on:     | Refer to:    |

|-----------------------------|--------------|

| Hardware Installation       | This Chapter |

| GtDio6x Driver Installation | This Chapter |

| Theory of Operation         | Chapter 4    |

# Interfaces and Accessories

The following accessories are available from Marvin Test Solutions the GX5960 series digital subsystem:

| Part / Model Number                                                                                                    | Description                                              |

|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| GT97110, DB9, sub D, 3' female power connector cable                                                                   | Supplies external power (Vcc ⋁) to the GX5964 and GX5961 |

| GT95014, Connector Interface for the GX5960, SCSI to 100 Mil Grid, Single Ended                                        | UUT I/O Interface, Analog Bus, Aux channels, HV I/O      |

| GT95015, Connector Interface for the GX5960, SCSI to 100 Mil Grid, Differential                                        | UUT I/O Interface, Analog Bus, Aux channels, HV I/O      |

| GT95015- SCSI, Connector Interface for the<br>GX5960, SCSI to 100 Mil Grid, Differential, no J2<br>connector installed | UUT I/O Interface, Analog Bus, Aux channels, HV I/O      |

| Connector I/F for GX5055, SCSI to 100 Mil Grid,<br>Single Ended (both 64 & 14 pin)                                     | UUT I/O Interface, Analog Bus, Aux channels, HV I/O      |

| GT95021, 2' shielded cable for GX5960 (68 Pin)                                                                         | UUT I/O Interface, Analog Bus, Aux channels, HV I/O      |

| GT95022, 3' shielded cable for GX5960 (68 Pin)                                                                         | UUT I/O Interface, Analog Bus, Aux channels, HV I/O      |

| GT95031, 6' shielded cable for GX5960 (68 Pin)                                                                         | UUT I/O Interface, Analog Bus, Aux channels, HV I/O      |

| GT95028,10' shielded cable for GX5960 (68 Pin)                                                                         | UUT I/O Interface, Analog Bus, Aux channels, HV I/O      |

# **Packing List**

All GX5960 boards have the same basic packing list, which includes:

- GX5961, GX5964/GX5964A Boards

- GtDio6x Software Disk

# **Unpacking and Inspection**

After removing the board from the shipping carton:

**Caution -** Static sensitive devices are present. Ground yourself to discharge static.

Remove the board from the static bag by handling only the metal portions.

Be sure to check the contents of the shipping carton to verify that all of the items found in it match the packing list.

Inspect the board for possible damage. If there is any sign of damage, return the board immediately. Please refer to the warranty information at the beginning of the manual.

# **System Requirements**

The GX5960 PXI digital subsystem is designed to run on 6U PXI compatible chassis running under XP or newer (32/64 bit).

Each board in the digital subsystem requires one unoccupied 6U PXI bus slot.

# Installation of the GtDio6X Software

Before installing the board it is recommended that you install the GtDio6x software as described in this section. To install the GtDio6x software, follow the instruction described below:

Insert the Marvin Test Solutions CD-ROM and locate the **GtDio6x.EXE** setup program. If you computer's Auto Run is configured, when inserting the CD a browser will show several options. Select the Marvin Test Solutions Files option and then locate the setup file. If Auto Run is not configured you can open the Windows explorer and locate the setup files (usually located under \Files\Setup folder). You can also check and see if a newer version of the software is available for download from Marvin Test Solutions' web site (<u>www.marvintest.com</u>), in that case download and use the newer version.

Run the GtDio6x setup and follow the instruction on the Setup screen to install the GtDio6x driver.

**Note:** When installing under Windows, you may be required to restart the setup after logging-in as a user with Administrator privileges. This is required in-order to upgrade your system with newer Windows components and to install kernel-mode device drivers (HW.SYS and HWDEVICE.SYS) which are required by the GtDio6x driver to access resources on your board.

The first setup screen to appear is the Welcome screen. Click Next to continue.

Enter the folder where GtDio6x is to be installed. Either click **Browse** to set up a new folder, or click **Next** to accept the default entry of C:\Program Files\Marvin Test Solutions\GtDio6x under 32-bit Windows or C:\Program Files (x86)\Marvin Test Solutions\GtDio6x under 64-bit Windows.

Select the type of Setup you wish and click **Next.** You can choose between **Typical**, **Run-Time** and **Custom** setups types. The **Typical** setup type installs all files. **Run-Time** setup type will install only the files required for controlling the board either from its driver or from its virtual panel. The **Custom** setup type lets you select from the available components.

The program will now start its installation. During the installation, Setup may upgrade some of the Windows shared components and files. The Setup may ask you to reboot after completion if some of the components it replaced were used by another application during the installation - do so before attempting to use the software.

You can now continue with the installation to install the board. After the board installation is complete you can test your installation by starting a panel program that lets you control the board interactively. The panel program can be started by selecting it from the Start, Programs, GtDio6x menu located in the Windows Taskbar.

# **Setup Maintenance Program**

You can run the Setup again after GtDio6x has been installed from the original disk or from the Windows Control Panel – Add Remove Programs applet. Setup will be in the Maintenance mode when running for the second time. The Maintenance window show below allows you to modify the current GtDio6x installation. The following options are available in Maintenance mode:

- Modify. When you want to add or remove GtDio6x components.

- Repair. When you have corrupted files and need to reinstall.

- Remove. When you want to completely remove GtDio6x.

Select one of the options and click Next and follow the instruction on the screen until Setup is complete.

# Overview of the GtDio6x Software

Once the software is installed, the following tools and software components are available:

- **GtDio6x Panel** Configures and controls the GtDio6x board various features via an interactive user interface.

- **GtDio6x driver** A DLL based function library (GTDIO6X.DLL for 32-bit applications or GTDIO6X64.DLL for 64-bit applications, located in the Windows System folder) used to program and control the board. The driver uses Marvin Test Solutions' HW driver or VISA supplied by third party vendor to access and control the GtDio6x boards.

- **Programming files and examples** Interface files and libraries for support of various programming tools. A complete list of files and development tools supported by the driver is included in subsequent sections of this manual.

- Documentation On-Line help and User's Guide for the board, GtDio6x driver and panel.

- HW driver and PXI/PCI Explorer applet HW driver allows the GtDio6x driver to access and program the supported boards. The explorer applet configures the PXI chassis, controllers and devices. This is required for accurate identification of your PXI instruments later on when installed in your system. The applet configuration is saved to PXISYS.ini and PXIeSYS.ini and is used by Marvin Test Solutions instruments HW driver. The applet can be used to assign chassis numbers, Legacy Slot numbers and instrument alias names. The HW driver is installed and shared with all Marvin Test Solutions products to support accessing the PC resources. Similar to HW driver, provides a standard way for instrument manufacturers and users to write and use instruments drivers. VISA is a standard maintained by the VXI Plug & Play System Alliance and the PXI Systems Alliance organizations (http://www.vxipnp.org/, http://www.pxisa.org/). The VISA resource manager such as National Instruments Measurement & Automation (NI-MAX) displays and configures instruments and their address (similar to Marvin Test Solutions' PXI/PCI Explorer). The GtDio6x driver can work with either HW or VISA to control an access the supported boards.

# **Installation Folders**

The GtDio6x driver files are installed in the default folder C C:\Program Files\Marvin Test Solutions\GtDio6x under 32-bit Windows or C:\Program Files (x86)\Marvin Test Solutions\GtDio6x under 64-bit Windows. During the installation, GtDio6x Setup creates and copies files to the following folders:

| Name                           | Purpose / Contents                                                                                                                                                                               |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \Marvin Test Solutions\GtDio6x | The GtDio6x folder. Contains panel programs, programming libraries, interface files and examples, on-line help files and other documentation.                                                    |

| \Marvin Test Solutions\HW      | HW device driver. Provide access to your board hardware resources such<br>as memory, IO ports and PCI board configuration. See the<br>README.TXT located in this directory for more information. |

| \ATEasy\Drivers                | ATEasy drivers folder. GtDio6x Driver and example are copied to this directory only if ATEasy is installed to your machine.                                                                      |

| Windows System Folders         | Contains the GtDio6x DLL and GtDio6x64.DLLdriver, HW driver shared files and some upgraded system components, such as the HTML help viewer, etc.                                                 |

# Configuring Your PXI System using the PXI/PCI Explorer

To configure your PXI/PCI system using the **PXI/PCI Explorer** applet follow these steps:

**Start the PXI/PCI Explorer applet**. The applet can be start from the Windows Control Panel or from the Windows Start Menu, **Marvin Test Solutions**, **HW**, **PXI/PCI Explorer**.

**Identify Chassis and Controllers**. After the PXI/PCI Explorer is started, it will scan your system for changes and will display the current configuration. The PXI/PCI Explorer automatically detects systems that have Marvin Test Solutions controllers and chassis. In addition, the applet detects PXI-MXI-3/4 extenders in your system (manufactured by National Instruments). If your chassis is not shown in the explorer main window, use the Identify Chassis/Controller commands to identify your system. Chassis and Controller manufacturers should provide INI and driver files for their chassis and controllers which are used by these commands.

**Change chassis numbers, PXI devices Legacy Slot numbering and PXI devices Alias names.** These are optional steps and can be performed if you would like your chassis to have different numbers. Legacy slots numbers are used by older Marvin Test Solutions driver. Alias names can provide a way to address a PXI device using a logical name (e.g. "FPGA1"). For more information regarding slot numbers and alias names, see the **GtDio6xInitialize** function.

**Save your work**. PXI Explorer saves the configuration to the following files located in the Windows folder: PXISYS.ini, PXIeSYS.ini and GxPxiSys.ini. Click on the **Save** button to save your changes. The PXI/Explorer will prompt you to save the changes if changes were made or detected (an asterisk sign '\*' in the caption indicated changes).

| E- A PXI System <ext< th=""><th>emal PC&gt;</th><th></th><th></th></ext<> | emal PC>                                                               |                                                              |             |

|---------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------|-------------|

| 🗄 🛄 Chassis 1 <                                                           | GX7000> <s :="" gx7000a-0<="" n="" th=""><th>063&gt;</th><th></th></s> | 063>                                                         |             |

|                                                                           |                                                                        | DI TURO DI L                                                 |             |

|                                                                           | GX5290 High-Speed Dynam<br>GTX2200 High Resolution U                   | niversal Time Interval Counter                               | Board       |

|                                                                           |                                                                        | TR [Status=Device is working p                               | 12210000000 |

| — A <mark>nSlo</mark>                                                     |                                                                        |                                                              | E           |

| i i i i i i i i i i i i i i i i i i i                                     | acy nSlot = 23<br>acy nSlot = 23                                       |                                                              |             |

| ⊡ Dev                                                                     |                                                                        |                                                              |             |

| 🗄 🗖 PXI                                                                   | Settings                                                               |                                                              |             |

|                                                                           |                                                                        | and Function Generator Board                                 |             |

|                                                                           | GX5296 Digital I/O with Pin<br>GX5961/4 Digital I/O Timin              | electronics and PMU Board<br>g / Sync with Pin Electronics a | nd PMU      |

|                                                                           | GX5295 Diaital L/O with Pin                                            | Electronice and PMII Roard                                   | *           |

| •                                                                         | III                                                                    |                                                              |             |

|                                                                           | Reset Chassis List                                                     | Scan for New Devices                                         | Save        |

| Display Options                                                           |                                                                        |                                                              |             |

Figure 3-1: PXI/PCI Explorer

# **Board Installation**

#### Before you Begin

- Install the GtDio6x driver as described in the prior section.

- Configure your PXI/PC system using **PXI/PCI Explorer** as described in the prior section.

- Verify that all the components listed in the packing list (see previous section in this chapter) are present.

#### **Electric Static Discharge (ESD) Precautions**

To reduce the risk of damage to the GX5960 board, the following precautions should be observed:

- Leave the board in the anti-static bags until installation requires removal. The anti-static bag protects the board from harmful static electricity.

- Save the anti-static bag in case the board is removed from the computer in the future.

- Carefully unpack and install the board. Do not drop or handle the board roughly.

- Handle the board by the edges. Avoid contact with any components on the circuit board.

**Caution** – Do not insert or remove any board while the computer is on. Turn off the power from the PXI chassis before installation.

#### **Chassis Requirements**

The GX5960 subsystem is compatible with any 6U PXI chassis that supports an air flow rate of 20 cfm/slot or greater. Power for the pin electronics requires the use of external power supplies or the GX5960 can be used with Marvin Test Solutions' **GX70005** or **GX7015** PXI chassis which is designed for the GX5960 and includes the necessary pin electronics' power supplies. The GX5960 can also be used with the **GX71xxBR-HP1** chassis which offers additional cooling and can support up to (4) GX960 modules, for low voltage / moderate performance applications. VCC and VEE power for this configuration can be supplied via an MTS GX7400A user power supply PXI module or external power supplies.

#### Board Installation in a GX70x5 PXI Chassis

The GX70x5 PXI chassis (Figure 3-2) is designed specifically for the **GX5055** and **GX5960** digital subsystems and includes additional power supplies for the digital subsystems' VCC, VEE and VDD voltages. Additionally, under software control via the GtDIO function library, the VCC and VEE voltages are programmed to the correct levels for the modules' programmed drive / sense levels, minimizing overall module power dissipation. The **GX70x5** chassis features (2) VCC programmable sources, providing additional flexibility for managing overall module power dissipation. VCC1 provides power to digital modules located in slots 4 - 11 and VCC2 provides power for slots 12 - 19, allowing the user to have two "families" of logic levels. VEE power is common to all slots, 4 - 19. Overall control / programming of the VCC and VEE power supplies is provided by a board (GX59611/4) which MUST be installed in slot 5. A board MUST also be installed in Slot 13 for enabling / disabling VCC2 which powers modules in slots 12 - 19.

Caution – on GX70x5 chassis A digital board MUST be installed in Slot 5 to control the programming of the VEE and VCC voltages

Figure 3-2: GX7005A Chassis

#### **Installing a Board**

Install the board as follows:

- 1. Install the GtDio6x software as described in the next section.

- 2. Turn off the PXI chassis and unplug the power cord.

- 3. Locate a PXI empty slot on the PXI chassis.

- 4. Place the module edges into the PXI chassis rails (top and bottom).

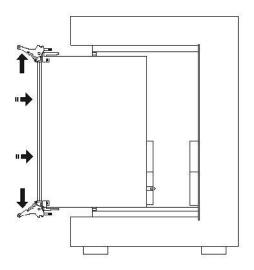

- 5. Carefully slide the PXI board to the rear of the chassis, make sure that the ejector handles are pushed out (as shown in Figure -32).

Figure 3-3: Ejector handle position during module insertion

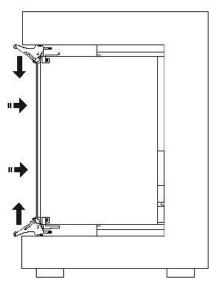

6. After you feel resistance, push in the ejector handles as shown in Figure 3-3 to secure the module into the frame.

Figure 3-4: Ejector handle position after module insertion

- 7. Tighten the module's front panel to the chassis to secure the module in.

- 8. Connect any necessary cables to the board.

- 9. Plug the power cord in and turn on the PXI chassis.

#### **Plug & Play Driver Installation**

Plug & Play operating systems such as Windows 9x, Me, Windows 2000, XP, VISTA or Windows 7 (Not Windows NT) notifies the user that a new board was found using the **New Hardware Found** wizard after restarting the system with the new board.

If another Marvin Test Solutions board software package was already installed, Windows will suggest using the driver information file: HW.INF. The file is located in your Program Files\Marvin Test Solutions\HW folder. Click **Next** to confirm and follow the instructions on the screen to complete the driver installation.

If the operating system was unable to find the driver (since the GtDio6x driver was not installed prior to the board installation), you may install the GTDIO6X driver as described in the prior section, then click on the **Have Disk** button and browse to select the HW.INF file located in C:\Program File\Marvin Test Solutions\HW.

If you are unable to locate the driver click **Cancel** to the found New Hardware wizard and exit the New Hardware Found Wizard, install the GtDio6x driver, reboot your computer and repeat this procedure.

The Windows Device Manager (open from the System applet from the Windows Control Panel) must display the proper board name before continuing to use the board software (no Yellow warning icon shown next to device). If the device is displayed with an error you can select it and press delete and then press F5 to rescan the system again and to start the New Hardware Found wizard.

#### **Removing a Board**

Remove the board as follows:

- 1. Turn off the PXI chassis and unplug the power cord.

- 2. Locate a PXI slot on the PXI chassis.

- 3. Disconnect and remove any cables/connectors connected to the board.

- 4. Un-tighten the module's front panel screws to the chassis.

- 5. Push out the ejector handles and slide the PXI board away from the chassis.

- 6. Optionally uninstall the GtDio6x driver.

# **Connectors and Jumpers**

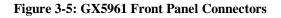

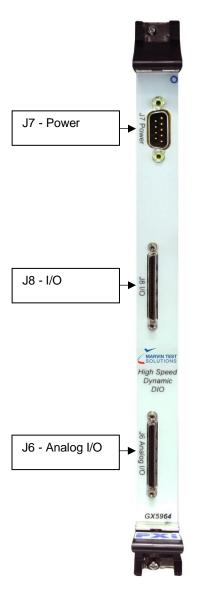

Figure 3-5 shows the available GX5964, GX5964A and GX5961 board connectors:

#### **GX5691 Connectors**

The GX5961 has 4 connectors. All the connectors are available on the instrument's front panel. The GX5961 has the following connectors:

| J7  | Power - VCC and VEE power connections for pin electronics. Not used if the GX5961 is installed in a GX70x5A chassis. |

|-----|----------------------------------------------------------------------------------------------------------------------|

| J8  | I/O - Programmable I/O Levels Data Connector Signals                                                                 |

| J6  | Analog I/O - 32 channel analog bus connections (connects to analog instrumentation / switch matrix)                  |

| J10 | High Voltage - 32 high voltage (open collector) outputs / inputs                                                     |

| J9  | Auxiliary Channels - External connections for clocking, external events and triggering                               |

Table 3-1: GX5961 Connectors

#### GX5694 Rev B Connectors

The GX5964 has 3 connectors. All the connectors are available on the instrument's front panel. The GX5964 has the following connectors:

| J7 | Power - VCC and VEE power connections for pin electronics. Not used if the GX5964 is installed in a Marvin Test Solution High Power chassis, e.g. GX70x5A/B/C chassis. |  |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| J8 | I/O - Programmable I/O Levels Data Connector Signals                                                                                                                   |  |

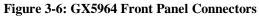

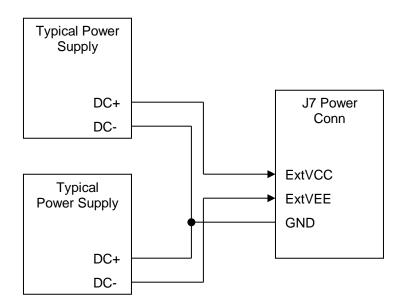

| J6 | Analog I/O - 32 channel analog bus connections (connects to analog instrumentation / switch matrix).                                                                   |  |

#### Table 3-2: GX5964 Connectors

#### **GX5694A Connectors**

The GX5964A has 4 connectors. All the connectors are available on the instrument's front panel. The GX5964A has the following connectors:

| J7 | Power - VCC and VEE power connections for pin electronics. Not used if the GX5964A is installed in a Marvin Test Solution tHigh Power chassis, e.g. GX70x5A/B/C chassis. |  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| P3 | I/O - Programmable I/O Levels Data Connector channels 1-16 Signals                                                                                                       |  |

| P2 | I/O - Programmable I/O Levels Data Connector channels 17-32 Signals                                                                                                      |  |

| J6 | Analog I/O - 32 channel analog bus connections (connects to analog instrumentation / switch matrix).                                                                     |  |

Table 3-3: GX5964A Connectors

### **GX5961 J7- Front Panel Power Connector**

The following table shows the power connector, J7, pin out. VCC supplied should be in the range of 10V to 29V, and VEE in the range of -3V to -20V.

| Pin No. | Signal   |

|---------|----------|

| 1       | ExtVCC   |

| 2       | ExtVCC   |

| 3       | ExtVEE   |

| 4       | ExtVEE   |

| 5       | Ext3.3V  |

| 6       | GND      |

| 7       | GND      |

| 8       | GND      |

| 9       | SHUTDOWN |

Table 3-4: J7 – GX5961 Front Panel Power Connector Pinout

The following Figure shows a typical connection to the Power connector:

#### Figure 3-8: GX5961 Typical Power Connection Diagram

**Note:** Ext. 3.3V (VDD) is supplied by the PXI backplane if the module is installed in GX7100-HP chassis. Under software control, the VDD power can be supplied via the J7 connector if the PXI chassis has insufficient 3.3V current.

# GX5961 J6- Front Panel Analog I/O Connector

| Pin# | Function | Pin# | Function               | Pin# | Function | Pin# | Function      |

|------|----------|------|------------------------|------|----------|------|---------------|

| 1    | N/C      | 18   | A_IO1                  | 35   | GND      | 52   | GND           |

| 2    | N/C      | 19   | A_IO2                  | 36   | GND      | 53   | GND           |

| 3    | N/C      | 20   | A_IO3                  | 37   | GND      | 54   | GND           |

| 4    | N/C      | 21   | A_IO4                  | 38   | GND      | 55   | GND           |

| 5    | N/C      | 22   | A_IO5                  | 39   | GND      | 56   | GND           |

| 6    | N/C      | 23   | A_IO6                  | 40   | GND      | 57   | GND           |

| 7    | N/C      | 24   | A_IO7                  | 41   | GND      | 58   | GND           |

| 8    | N/C      | 25   | A_IO8                  | 42   | GND      | 59   | GND           |

| 9    | N/C      | 26   | A_IO9                  | 43   | GND      | 60   | GND           |

| 10   | N/C      | 27   | A_IO10                 | 44   | GND      | 61   | GND           |

| 11   | N/C      | 28   | A_I011                 | 45   | GND      | 62   | GND           |

| 12   | N/C      | 29   | A_IO12                 | 46   | GND      | 63   | GND           |

| 13   | N/C      | 30   | A_IO13                 | 47   | GND      | 64   | GND           |

| 14   | N/C      | 31   | A_IO14                 | 48   | GND      | 65   | GND           |

| 15   | N/C      | 32   | A_IO15                 | 49   | GND      | 66   | GND           |

| 16   | N/C      | 33   | USER SCLK              | 50   | GND      | 67   | USER<br>SDATA |

| 17   | A_I00    | 34   | USER<br>SDATA<br>VALID | 51   | GND      | 68   | NC            |

Each of the Analog I/O channels has a relay for isolating the Pin Electronics from the DUT.

Table 3-5: J6 – GX5961 Front Panel Analog I/O Connector Pinout

# GX5961 J8- Front Panel I/O Connector

| Pin# | Function | Pin# | Function         | Pin# | Function | Pin# | Function  |

|------|----------|------|------------------|------|----------|------|-----------|

| 1    | N/C      | 18   | CH1              | 35   | GND      | 52   | GND       |

| 2    | N/C      | 19   | CH2              | 36   | GND      | 53   | GND       |

| 3    | N/C      | 20   | CH3              | 37   | GND      | 54   | GND       |

| 4    | N/C      | 21   | CH4              | 38   | GND      | 55   | GND       |

| 5    | N/C      | 22   | CH5              | 39   | GND      | 56   | GND       |

| 6    | N/C      | 23   | CH6              | 40   | GND      | 57   | GND       |

| 7    | N/C      | 24   | CH7              | 41   | GND      | 58   | GND       |

| 8    | N/C      | 25   | CH8              | 42   | GND      | 59   | GND       |

| 9    | N/C      | 26   | CH9              | 43   | GND      | 60   | GND       |

| 10   | N/C      | 27   | CH10             | 44   | GND      | 61   | GND       |

| 11   | N/C      | 28   | CH11             | 45   | GND      | 62   | GND       |

| 12   | N/C      | 29   | CH12             | 46   | GND      | 63   | GND       |

| 13   | N/C      | 30   | CH13             | 47   | GND      | 64   | GND       |

| 14   | N/C      | 31   | CH14             | 48   | GND      | 65   | GND       |

| 15   | N/C      | 32   | CH15             | 49   | GND      | 66   | GND       |

| 16   | N/C      | 33   | N/C              | 50   | GND      | 67   | N/C       |

| 17   | СНО      | 34   | EXFORCE<br>VALID | 51   | GND      | 68   | FP-DUTGND |

Each of the I/O channel has a relay for isolating the Pin Electronics from the DUT.

Table 3-6: GX5961 J8 - Front Panel I/O Connector Pin out

| Pin# | Function | Pin# | Function | Pin# | Function | Pin# | Function |

|------|----------|------|----------|------|----------|------|----------|

| 1    | AUX0     | 18   | GND      | 35   | GND      | 52   | GND      |

| 2    | AUX1     | 19   | GND      | 36   | GND      | 53   | GND      |

| 3    | AUX2     | 20   | GND      | 37   | GND      | 54   | GND      |

| 4    | AUX3     | 21   | GND      | 38   | GND      | 55   | GND      |

| 5    | AUX4     | 22   | GND      | 39   | GND      | 56   | GND      |

| 6    | AUX5     | 23   | GND      | 40   | GND      | 57   | GND      |

| 7    | AUX6     | 24   | GND      | 41   | GND      | 58   | GND      |

| 8    | AUX7     | 25   | GND      | 42   | GND      | 59   | GND      |

| 9    | AUX8 +   | 26   | GND      | 43   | AUX8 -   | 60   | GND      |

| 10   | AUX9 +   | 27   | GND      | 44   | AUX9 -   | 61   | GND      |

| 11   | AUX10 +  | 28   | GND      | 45   | AUX1 -   | 62   | GND      |

| 12   | AUX11 +  | 29   | GND      | 46   | AUX11 -  | 63   | GND      |

| 13   | GND      | 30   | GND      | 47   | PBUT     | 64   | GND      |

| 14   | GND      | 31   | GND      | 48   | PLED+B   | 65   | GND      |

| 15   | GND      | 32   | GND      | 49   | PCLK+B   | 66   | GND      |

| 16   | GND      | 33   | GND      | 50   | GND      | 67   | GND      |

| 17   | GND      | 34   | GND      | 51   | GND      | 68   | GND      |

GX5961 J9- Front Panel Auxiliary Channels Connector

Table 3-7: GX5961 J9 - Front Panel Auxiliary Channels Connector Pinout

| Pin# | Function | Pin# | Function        | Pin# | Function | Pin# | Function |

|------|----------|------|-----------------|------|----------|------|----------|

| 1    | HV_PINS  | 18   | HV_PINS         | 35   | GND      | 52   | GND      |

| 2    | HV_PINS  | 19   | HV_PINS         | 36   | GND      | 53   | GND      |

| 3    | HV_PINS  | 20   | HV_PINS         | 37   | GND      | 54   | GND      |

| 4    | HV_PINS  | 21   | HV_PINS         | 38   | GND      | 55   | GND      |

| 5    | HV_PINS  | 22   | HV_PINS         | 39   | GND      | 56   | GND      |